현재 1차 작성(21년 9월)

물리에 대해 자세히 설명하고 싶지만 주제가 전자회로 파트이니 동작 중심으로 어떻게 돌아가나 위주로 이 글을 적게 되었습니다.

정성적인 해석을 위주로 이에 대한 결과에 대한 수식으로 적는 것으로 구성하였습니다.

시간이 남으면 2차 개정을 통해 정량적인 해석도 추가

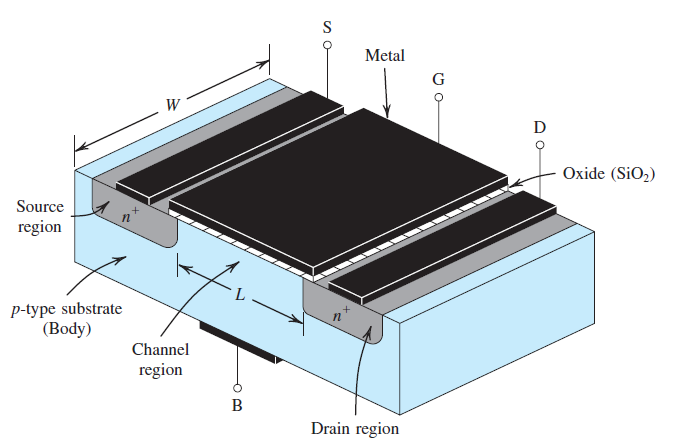

MOSFET 구조

이후에 등장할 식과 원리를 이해하기 위해 MOSFET의 구조는 아래와 같다.

여기서 봐야할 것은 W는 MOSFET의 폭, L은 MOSFET의 n+로 도핑된 소스와 드레인 단자의 거리이다.

MOSFET의 동작 영역

간단하게 아래의 표. 1과 같이 간단하게 동작을 나누어 표현이 가능하다.

표 1. 동작 조건과 이름

| 구분 | 해당 영역의 동작 조건 | 전류의 함수(2차 효과 고려x) | 전류의 함수(2차 효과 고려) |

| Cut-off (전원이 꺼진 상태) | Vgs<Vth | 없음, 꺼져있기 때문 | 없음, 꺼져있기 때문 |

| Triode(트라이오드) | Vgs-Vth>Vds | Vgs와 Vds | Vgs와 Vds |

| Saturation(포화) | Vgs-Vth=<Vds | Vgs | Vgs와 Vds(채널 길이 변조 때문에) |

트랜지스터의 동작을 해석할 때에는 I/V 커브 즉 전압 변화에 따른 전류의 결과가 중요함을 먼저 인지해야하고

BJT, MOSFET같은 트랜지스터의 I/V 커브를 이해할 때 두가지 종류의 I/V 커브를 이해해야한다.

첫번째는 게이트 전압 변화에 따른 전류의 변화(이 때 드레인 전압은 충분히 크다고 가정)

두번째는 드레인 전압 변화에 따른 전류의 변화(이 때 게이트 전압은 충분히 크다고 가정)

Cut-off

(Vgs <= Vth & Vgs > Vth)

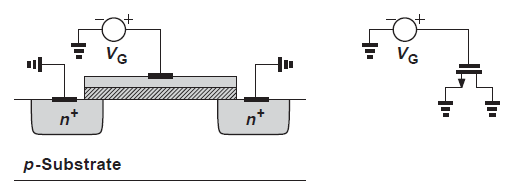

Vgs=0 일 때 (참고 : Vgs의 뜻은 게이트와 소스의 전압차이 즉 Vg-Vs=Vgs 이라는 의미이다.)

Vgs, Vgd 대문자 영어의 아랫첨자는 두 단자간의 전압차를 의미하는 것이다. 이 전압차를 이해해야 회로의 전반적인 해석이 가능하게 되는데.

지금 이 포스팅에서는 소스 단자는 접지에 연결이 되어있어 0V가 된다. 그러면 Vgs=Vg-0이 되며, Vgd는 게이트와 드레인의 전압 차이를 이야기 한다.

게이트에 0V의 전압이 인가되었을 때, 드레인과 소스 사이에는 애노드를 서로 맞댄 두 다이오드가 직렬로 존재하게 된다.

이 때 드레인 전압이 0 이상이 되어도 다이오드의 역방향이기 때문에 드레인에서 소스로 전류 전도를 막게 된다.

0<Vgs<Vth , Vds=0

게이트의 양전하는 기판(P-substrate)에서 정공을 쫓아내 기판에서 음이온들이 노출되어 공핍층을 형성한다.

Vgs>Vth, Vds=0

게이트 전압이 증가하면서 많은 음이온들이 노출되며 산화물 밑의 공핍 영역이 더 깊어진다. 이 때 문턱전압(Vth)보다 커지게 되면 자유 전자들이 산화물-실리콘 계면으로 끌어당겨지고 전도성 채널이 생성된다.

이때 게이트에 있는 산화물-실리콘 계면은 하나의 커패시터로 동작하게 되고 드레인에서 소스로 흐르는 전류는 아직 없다.

따라서 Vds를 증가시킴으로써 전류를 흘릴 수 있으니 Triode와 Saturation 영역을 살펴본다.

Triode Region(트라이오드 영역, 선형 영역)

(Vgs-Vth > Vds)

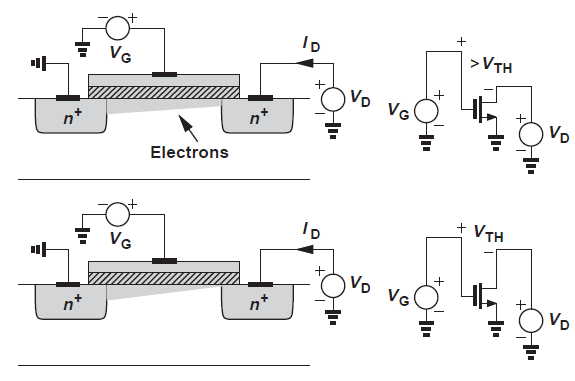

Cut Off에서 우리는 드레인 전압(Vd)에 전압을 인가하지 않고, 게이트 전압 Vg를 문턱전압(Vth)보다 높게 키웠을 때 채널이 형성됨을 알았다.

들어가기에 앞서 드리프트와 확산으로 인한 두가지 현상 때문에 전하의 흐름을 알 수 있다.

MOSFET에서는 드리프트에 의한 전류 생성이다.

I/Vds(드레인 전압 변화에 따른 전류 변화)

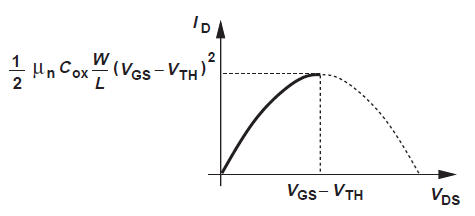

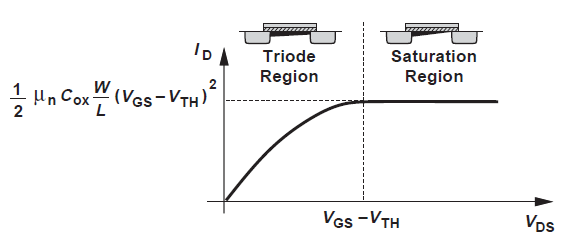

트라이오드 영역에서 드레인의 전류는 포물선의 형태로 전류가 증가하게 되는데 Vds가 과구동 전압(Vgs-Vth=Vov)과 동일한 값, 즉 최대값이 되면 전류는 증가하지 않는다(채널길이변조를 제외한다고 가정)

이러한 이유는 채널 내부에 의해 생기는 저항성분으로 인해 드레인과 소스의 전압차로 드레인으로 갈 수록 전압이 점점 증가하게 된다.

다르게 표현하면 소스단자에는 접지에 연결되어 0V이지만 Vgs=Vg-Vs Vg의 값만 존재한다.

채널에서 전압을 측정한다고 생각하고 소스에서의 전압은 0, 드레인 쪽으로 전압을 측정할 때 드레인 단자로 갈수록 전압이 조금씩 증가하여 드레인에 도착했을때는 Vgd=Vg-Vd가 된다.

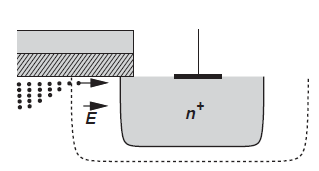

이해가 안갔다면, 다시 Cut off를 생각해보자 기존에 드레인 전압을 인가하지 않았기 때문에 Vgd(=Vg-0)>Vth보다 컸기 때문에 채널이 형성이 되었는데 드레인 전압이 인가되면 Vgd<Vth가 될 수 있기 때문에 드레인 단자 n+영역 도핑된 영역 옆 채널이 없어지기 시작하게 되며 공핍층으로 덮여지게 된다. 이러한 현상을 핀치 오프(Pinch-off)라고 표현한다.

공핍영역으로 덮이게 되면 전류가 흐르지 않는다라고 생각할 수 있지만 이 공핍영역에는 강한 전기장이 형성이 되기 때문에 채널 끝에 있는 전자는 드리프트 현상에 의해 쓸려나가게 된다.

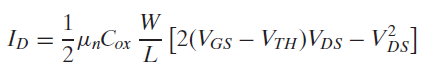

따라서 핀치 오프 이전의 전류는 식 1과 같이 표현할 수 있다.

여기서 mu와 Cox는 공정 상수, W는 MOSFET의 게이트의 폭, L은 MOSFET의 길이이다.

공정상수는 반도체 스케일에 따라 달라지며, 회로를 설계할 때 전류를 변화시켜줄 수 있는 요소는 과구동 전압, Vds, W/L이 된다.

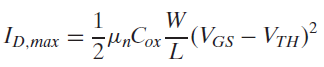

과구동 전압이 핀치오프에 있게 되면 드레인 전류는 식 2와 같이 표현이 가능하다.

이러한 Vds 변화에 의해 생기는 드레인 전류의 결과는 사진 6처럼 표현된다.

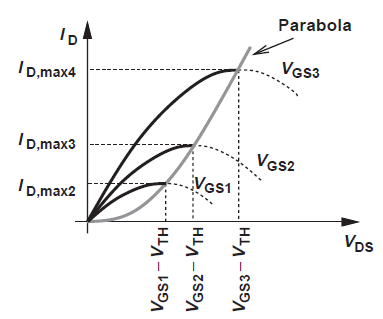

I/Vgs(게이트 전압 변화에 따른 전류 변화)

Vds가 일정하고 Vgs를 변화시켰을 때는 위에서 언급한 Cut off와 I/Vds의 변화에서 이해했다면 이 변화는 간단하다.

게이트의 전압의 변화를 주면 채널은 더 깊게 형성이 되며, 더 높은 전류를 흐르게 할 수 있다.(식 1,2 참조)

따라서 게이트 전압 변화에 다른 드레인 전류의 결과는 사진 7처럼 표현이 가능하다.

Saturation Region(포화 영역)

Vov<Vds

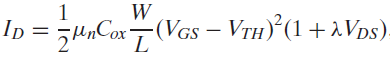

채널길이변조(Channel Length Modulation)을 고려하지 않고 I/Vds를 고려하면 식 2와 동일한 드레인 전류를 흐르게 한다.

채널길이변조

핀치오프에서 드레인의 전압이 높아질수록 L의 길이가 짧아짐을 알 수 있는데 결국엔 식 2에서 L은 감소하게 된다.

채널길이변조의 영향을 고려하기 위해 보정 항을 곱해주어 전류의 식을 표현할 수 있다.

식 3에서 람다(Lambda)는 채널길이변조 계수이고, 전류는 드레인전압과, 게이트 전압의 함수로서 표현하게 될 수있음을 확인했고 채널길이변조를 고려한 I/Vds를 고려하면 아래와 같다.

해당 정리는 다시 위로 올라가서 표1을 참고하면 된다.

개선해야될 사항

정량적인 해석, 나중에 살을 더 붙여 표현하기

전자회로 1 과정을 학습하셨습니다.

아래 링크를 통해 다음 진도와 전자회로 1의 모든 내용을 확인하실 수 있습니다.

2022.01.13 - [전공(Major)/전자회로 1 과정] - 전자회로 1 커리큘럼

전자회로 1 커리큘럼

전자회로 1 커리큘럼입니다. 기본적으로 반도체 공학에서 배웠던 능동소자(Diode, BJT, MOSFET)를 통해 단일 증폭기를 설계한다. 회로를 해석하는데에 있어 회로이론에서 배운 회로 해석기법을 사용

doctorinformationgs.tistory.com

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 소신호 등가모델(Small Signal Equivalent Model)에 알아보자 (0) | 2021.10.09 |

|---|---|

| 다이오드 회로의 일정전압모델 해석 (4) | 2021.10.02 |

| 이상적인 다이오드 회로의 이해(회로기초, 측정을 통해 이해해보자) (0) | 2021.10.02 |

| 밀러 이론(Miller Theorem) (0) | 2021.09.15 |

| 아날로그 회로설계 개요 (0) | 2021.09.01 |

댓글