CS amp에 대한 자세한 설명은 아래 링크에서 다룹니다!

https://contents.premium.naver.com/informationgs/takeinformationgs/contents/240208151552395ex

[전자회로 1] MOS 바이어스 회로

해당 영상은 아래 포스트에 담겨진 내용과 전자회로 1에서 MOS 증폭기 중 바이어스 회로에 대해서 다룹니다. https://doctorinformationgs.tistory.com/290 결제후 영상과 필기를 볼 수 있습니다.

contents.premium.naver.com

공통 소스 증폭기(Common Source Amplifier)

https://contents.premium.naver.com/informationgs/takeinformationgs/contents/240212193446947tr

[전자회로 1] 공통 소스 증폭기 (Common-Source Amplifier)

해당 영상은 아래 포스트에 담겨진 내용과 전자회로 1에서 MOS 증폭기 중 공통 소스단에 대해서 다룹니다. https://doctorinformationgs.tistory.com/290 결제후 영상과 필기를 볼 수 있습니다.

contents.premium.naver.com

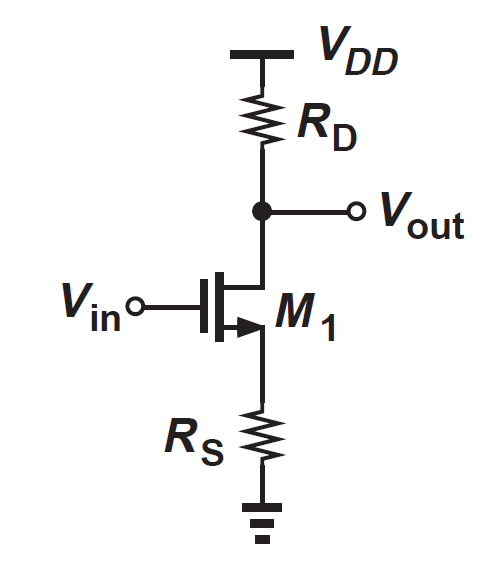

구 조

공통 소스 증폭기는 V/I 변환(MOSFET의 특성) + I/V 변환(저항)의 조합이다.

이게 무슨말이냐? 게이트에 인가된 전압에 따라 전류를 만들고, 만들어진 전류가 저항에 전압강하(V=IR)를 통해 나오는 결과를 의미하게 된다.

아래 사진 1을 통해 어떤 구조인지 확인해 볼 수 있다. 저항 아랫 첨자의 의미는 드레인(Drain)의 앞 글자를 딴 것이다.

대신호 해석

출력 전압은 식 1로 표현이 되며 게이트의 전압(Vin)을 증가하였을 때 생기는 변화는 사진 2와 같다.

식 1을 통해 알 수 있는 것은 드레인 저항의 전압강하가 드레인 전류에 비례하기 때문에 Vin이 증가하면 출력 전압이 감소함을 알 수 있다.

1) 문턱전압 보다 낮을 때

MOS가 전원이 켜져있지 않기 때문에 개방회로로 동작하여, 출력 전압은 Vout과 같다.

2) 문턱전압보다 높을 때

MOS 내부에 채널이 형성이 되고 전류가 흐르기 시작하면서 드레인쪽 저항의 전압강하가 생겨 출력 전압이 떨어지기 시작한다.

그러면 Vout의 전압을 구하는 이유가 무엇일까? 라는 의문점이 생겨야한다.

사진 1에서 구해지는 출력 전압은 결국 드레인-소스의 전압을 구하는 것과 같다.(Vds=Vout)

그러면 드레인-소스 전압을 구하는건 알겠는데 드레인-소스 전압은 왜 구하는 것일까?

이 말은 드레인-소스 전압이 너무 낮게 되면 MOS가 트라이오드 영역에 동작할 수 있기 때문에 확인을 해보아야 한다.

*대신호에서의 채널길이 변조

채널길이 변조는 소신호 해석에 더 중요하기 때문에 생략하고 바이어스 점(Bias Point)를 보는게 계산하기 편하다 고려하지 않아도 이 지점은 나름 정확하니 고려하지 않는게 좋다.

증명 방법은 KVL을 VDD-RD-Vout 루프를 만들어 알 수 있다.

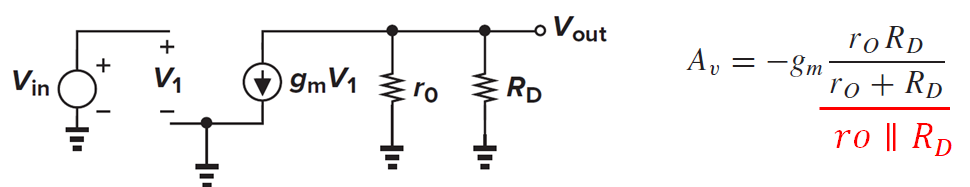

소신호 해석

소신호 등가회로에서의 전압이득을 구할 때는 KCL, KVL을 이용해서 구할 수 있지만 CS에서 식 1을 미분함으로써 식 2의 전압이득을 얻을 수 있습니다.

채널길이 변조를 고려안한 식 2를 통해 알 수 있는점은 gm을 키우거나 드레인 저항(부하 저항)의 값을 키우면 전압이들을 키울수 있습니다.

식 2에서 전압이득이 마이너스(-)의 부호를 가지고 있는데 이는 위상이 반전이 됨을 알아야 합니다.

채널길이 변조를 고려하면 아래와 같습니다.

식 3에서 알 수 있는 것은 ro와 부하저항의 병렬조합으로 표현이 가능합니다.

응용 회로

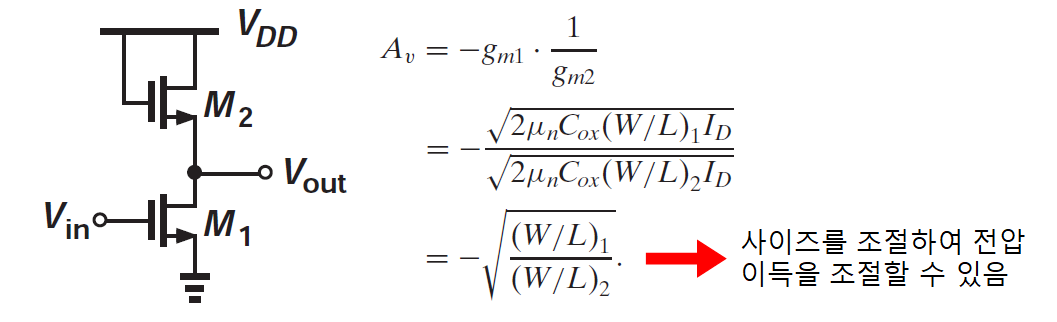

1. Diode Connected Load(다이오드 연결 부하)

다이오드 소신호 해석에서 다이오드의 소신호 등가모델은 하나의 저항으로써 표현이 되었음을 알고있다면 조금 더 이해하기 쉬울 수 있습니다.

Diode Connected Load 같은 경우 M2의 출력 임피던스가 1/gm2로 보이게 되며, 다이오드 소신호 등가모델과 비슷하게 표현이 가능하기 때문에 위와 같은 이름을 정해주게 된 것이죠

다이오드 연결 부하 같은 경우 작은 공정 스케일링에서 저항에 비해 훨씬 작기 때문에 칩의 면적을 고려하면 아주 좋은 선택일 수 있습니다.

전압이득은 결국 M1과 M2의 gm에 따라 정해짐을 알 수 있는데 위 식 4를 보게되면 결국 전압이득은 M1의 W/L, 즉 MOSFET의 사이즈에 따라 결정됨을 알 수 있습니다.

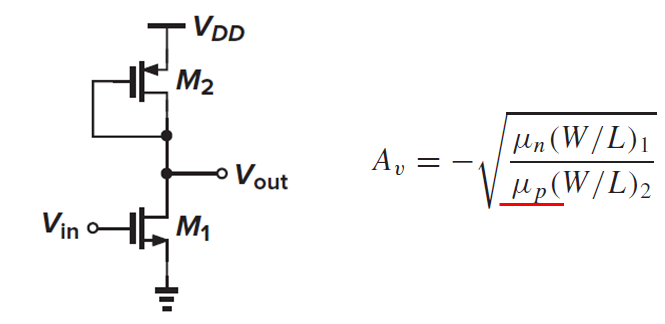

추가적으로 M2를 NMOS 대신에 PMOS로 조절이 가능하기도 합니다. 식 5에서 알 수 있는 점음 PMOS의 이동도(mu)는 NMOS보다 낮으니 더 높은 전압 이득을 취할 수 있습니다.

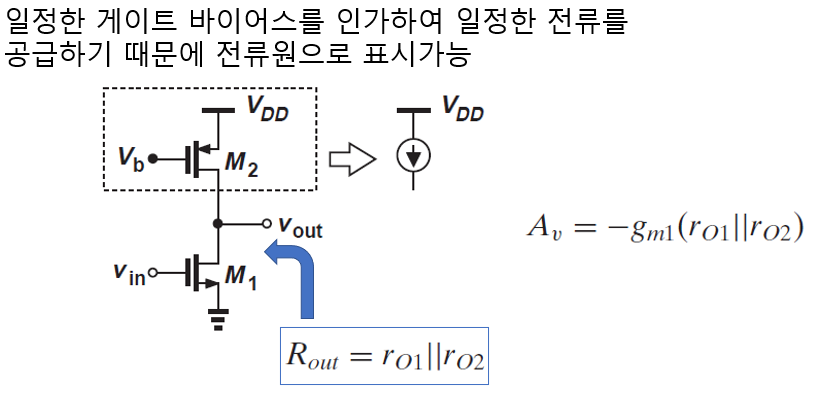

2. 전류원 부하를 가지는 CS 증폭기

공통소스 증폭기와 저항의 조합은 gm을 키우거나, 드레인의 저항을 키움으로써 전압 이득을 키울 수 있음을 알 수 있었습니다.

gm을 키우면 전류소모가 증가하여 회로의 전력소모가 커지는 문제점과 부하저항의 값을 너무 키우게 되면 트랜지스터가 트라이오드 영역에서 동작하게 되는 문제점이 발생하게 되죠

따라서 이 문제점을 해결하고자 나온 것이 전류원 부하를 가지는 공통소스 증폭기 입니다.

나중에 캐스코드라는 구조로 전압이득을 더 뻥튀기 할 수 있는 구조도 있지만 출력에서 바라보는 임피던스가 M1, M2의 저항성분이 보이게 됩니다. ro 저항은 매우 큰 값을 가질수 있고, 저항보다 작은 면적, 더 높은 값을 사용 가능하게 됩니다. M1이 트라이오드에서 동작하는 문제를 M2의 소스-드레인 전압강하만 고려하면됩니다.

전압이득은 M1의 트랜스컨덕턴스와 ro1,2 저항의 병렬 연결이 나오게 됩니다.

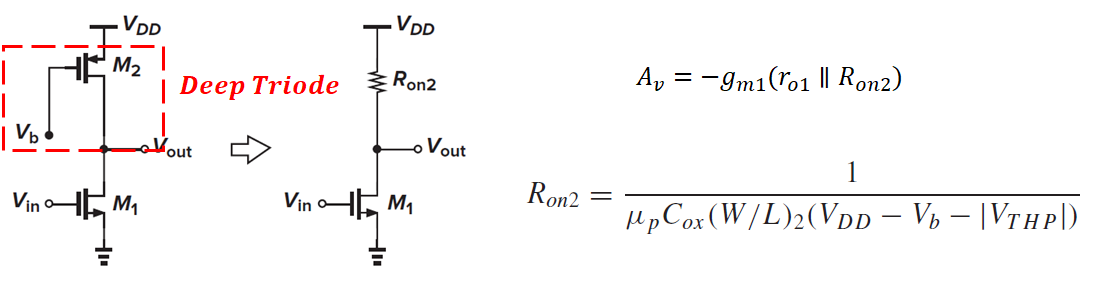

3. 트라이오드 부하를 가지는 CS 증폭기(많이 중요한 구조는 아님)

응용 2에서의 전류원에서의 동작은 포화영역에서 동작하고 있고, 응용 3은 트라이오드 영역에서 동작하게 되는데 여기서 동작영역을 트라이오드 영역 중 Deep 트라이오드 영역에서 동작을 하게되는겁니다.

식 9를 통해 알 수 있는 점은 ro와 온 저항의 병렬 조합으로 표현이 가능하다.

4. 소스 축퇴(또는 감생) 저항을 가지는 CS (Source Degeneration Resistor CS)

(이 중요한 부분이라 증명을 많이 함)

https://contents.premium.naver.com/informationgs/takeinformationgs/contents/240212193953707hy

[전자회로 1] 축퇴를 가지는 공통 소스단 (CS stage with degeneration)

해당 영상은 아래 포스트에 담겨진 내용과 전자회로 1에서 CS amp중 축퇴 저항이 있는 경우에 대해서 다룹니다. https://doctorinformationgs.tistory.com/290 결제후 영상과 필기를 볼 수 있습니다.

contents.premium.naver.com

트랜스컨덕턴스의 의미를 이해하기 어려우신 분들은 아래 링크를 참조하여 이해하기에 도움이 됩니다

2021.10.09 - [회로 해석 기초 지식/Basic] - 트랜스컨덕턴스(gm)의 의미

트랜스컨덕턴스(gm)의 의미

Transconductance(트랜스컨덕턴스) 왜 알아야 할까? 능동 소자(BJT, MOSFET)같은 소신호 회로해석에서 트랜스 컨덕턴스는 항상 나온다. 이번 포스팅에선 그 의미를 여러 책들을 참고하여 자세히 설명하

doctorinformationgs.tistory.com

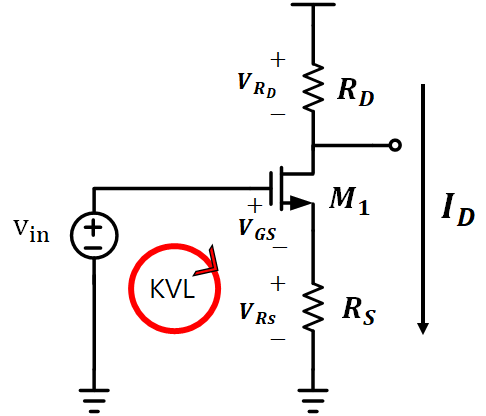

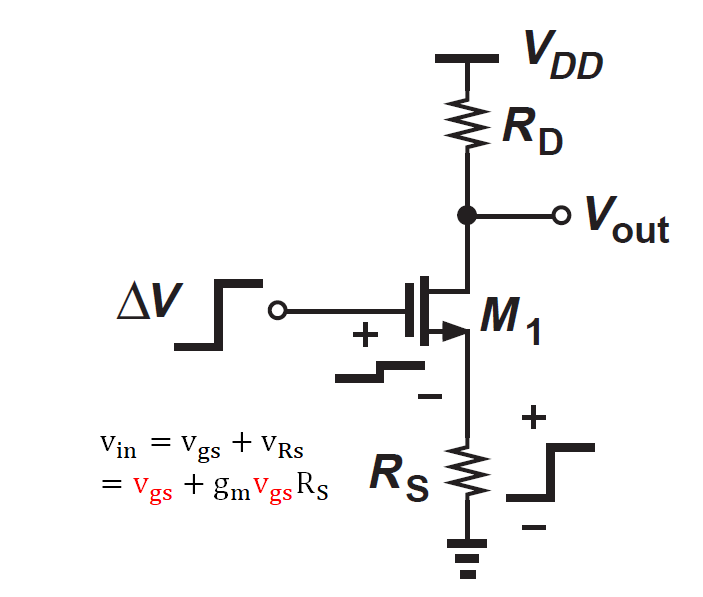

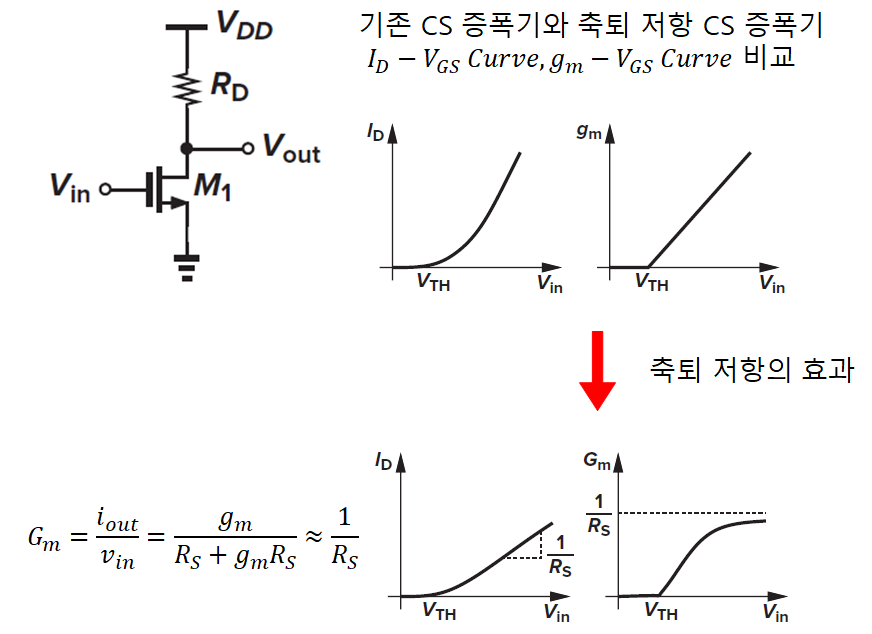

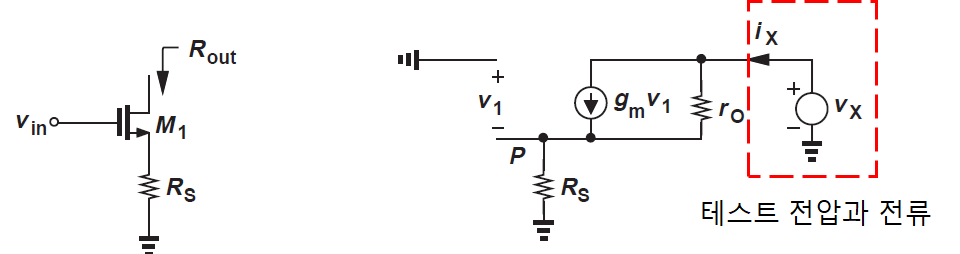

구조를 먼저 보자 소스에 저항이 달려 있음을 확인할 수 있는데, 이 축퇴 저항을 달아줌으로써 비선형인 능동소자를 보다 선형적으로 만들어 줄 수있는 장점이 있다.

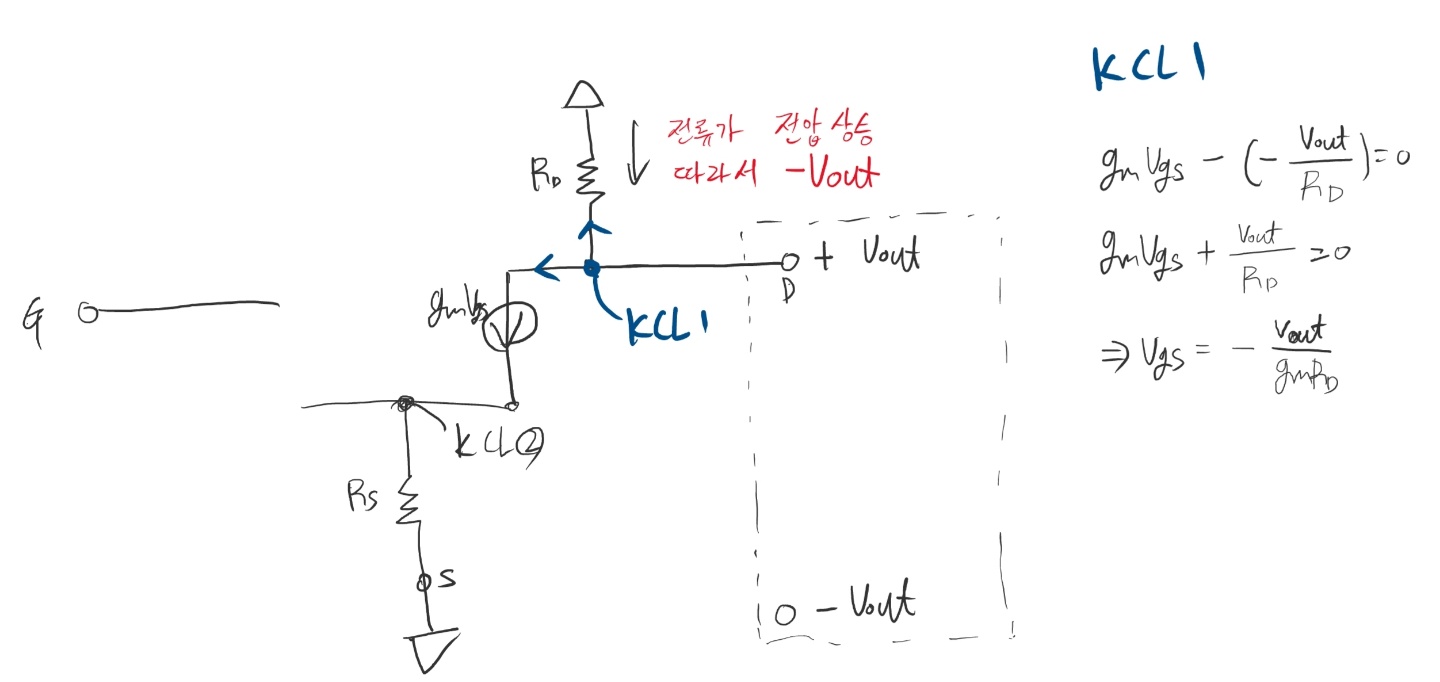

축퇴 저항을 해석하기 위한 첫번째 절차로 각각의 소자가 전압강하를 얼마나 가지는지에 대해서 알아야 한다.

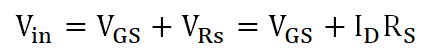

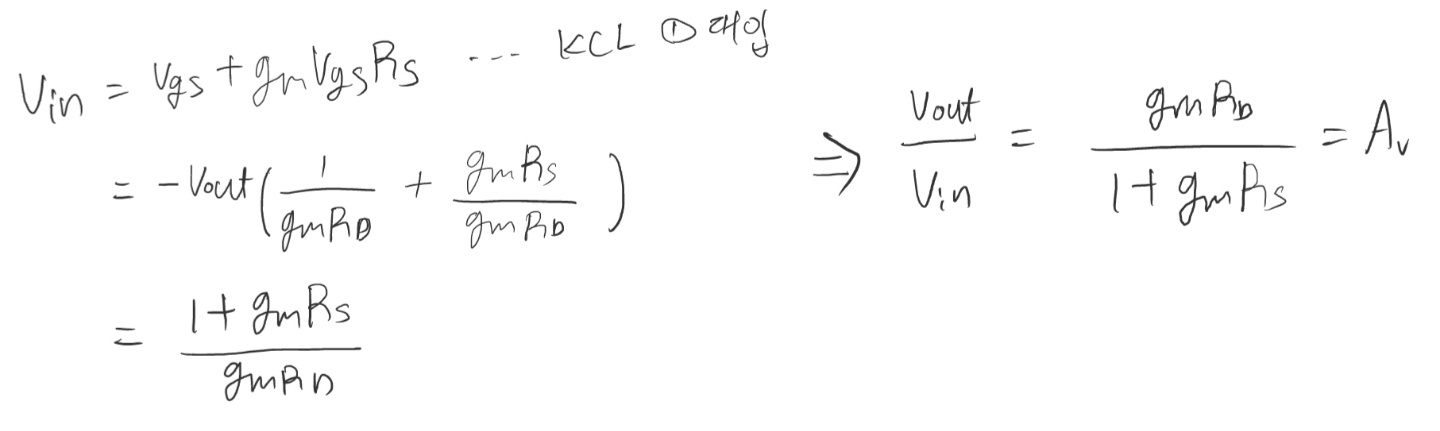

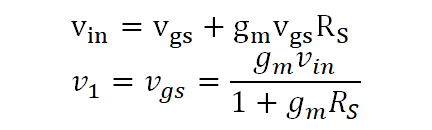

입력 쪽에 KVL을 적용하면 아래와 같다.

식 10을 통해서 알 수 있었던 것은 기존에 입력 전압이 VGS와 동일했지만 축퇴 저항의 전압강하의 성분이 더 들어감을 알 수 있다.

소신호 등가 모델을 통해서 Vgs에 대해 계산을 해보면 아래와 같다.

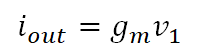

식 10의 드레인 전류는 소신호 모델에서 gmVgs임으로 전압이득을 계산하면 아래와 같은 연산과정을 거치는데

우리는 이 연산과정에서 축퇴저항이 어떤 역할을 하는지에 대해 알 수 있다.

사진 13에서 전압이득의 위상은 (-) 부호인데 실수로 안적었네요 참고하시기 바랍니다.

무슨 역할을 하는지에 대해 더 자세히 알아보자 입력 전압을 증가 시켰을때 소스에 있는 가지(Branch)의 전압 변화량을 볼 때 MOSFET의 게이트-소스 전압은 작은 변화를 일으키지만 축퇴저항의 전압강하는 gmRs배 만큼 더 큰 전압 변화량이 결과적으로 나오게 된다.

따라서 전류의 변화량은 결국엔 (전류 할당)

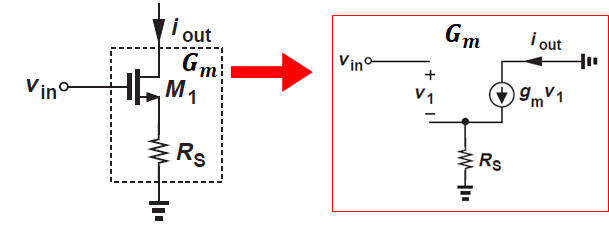

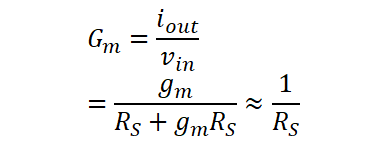

선형성의 증가를 확인하기 위해 사진 14의 구조를 Gm이라 표현하고, 전압 변화에 따른 전류의 변화 즉 축퇴 저항을 포함한 트랜스컨덕턴스는 아래와 같이 표현 가능하다.

사진 14와 식 13을 통해 알 수 있는 점은 전압 변화에 따른 전류의 결과가 결국 축퇴 저항이 대부분 할당함을 알 수 있다.

선형성이 어떻게 좋아지는지는 사진 15를 통해 알 수 있다.

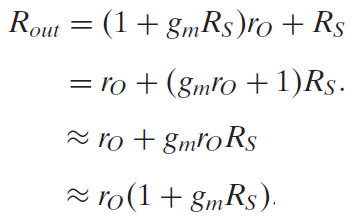

축퇴 저항을 가진 cs 증폭기는 출력 저항을 증가시켜주는 것 장점이 하나 더 있다.

기존에 기존 CS stage 즉 MOSFET 드레인에서 보는 저항은 ro임을 알 수 있습니다만 축퇴저항을 추가한 CS stage의 출력 저항은 아래의 과정에서 알 수 있습니다.

입출력 임피던스를 구하는데에 어려움이 있으셨다면 아래의 링크를 통해 이해를 하는데에 도움을 얻으시기 바랍니다.

2021.10.07 - [회로 해석 기초 지식/Basic] - 입출력 임피던스는 왜 필요할까?

입출력 임피던스는 왜 필요할까?

의문점 학부시절에서 어디에서 보는 임피던스를 항상 물어본 것이 기억이 난다. 회로이론에서는 어떤 두 노드에서 보이는 임피던스, 전자회로에서는 입력과 출력 임피던스를 항상 구하게 된다.

doctorinformationgs.tistory.com

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 차동증폭기의 대신호와 소신호해석 (0) | 2021.10.15 |

|---|---|

| 단일 증폭기와 차동 증폭기의 차이점과 장단점 정리 (0) | 2021.10.13 |

| 소신호 등가모델(Small Signal Equivalent Model)에 알아보자 (0) | 2021.10.09 |

| 다이오드 회로의 일정전압모델 해석 (4) | 2021.10.02 |

| 이상적인 다이오드 회로의 이해(회로기초, 측정을 통해 이해해보자) (0) | 2021.10.02 |

댓글