차동 증폭기에 대한 포스팅은 여러 차례에 걸쳐 작성이 되고 있습니다.

이해를 하기 어렵다면 아래의 링크를 참조해주세요

제일 먼저 쓴 글

2021.10.13 - [전공(Major)/전자회로와 아날로그 회로설계] - 단일 증폭기와 차동 증폭기의 차이점과 장단점 정리

단일 증폭기와 차동 증폭기의 차이점과 장단점 정리

이번 포스팅은 차동증폭기를 제대로 이해하는데에 앞서 에피타이져의 식으로 장단점과 단일 증폭기에 대한 차이점을 이해하도록 하기 위함과 차동증폭기 본문의 분량이 많아질 것을 우려해 해

doctorinformationgs.tistory.com

두번째 진도

2021.10.15 - [전공(Major)/전자회로와 아날로그 회로설계] - 차동증폭기의 대신호와 소신호해석

차동증폭기의 대신호와 소신호해석

본 포스팅을 하기에 앞서 저항의 값, 트랜지스터의 사이즈(W/L)이 모두 동일하다고 가정하여 풀이를 시작합니다. 이전 진도에 대한 복습 단일 출력과 차동 출력에 대해 생기는 이점과 단점에 대

doctorinformationgs.tistory.com

이 글은 세번째 진도입니다.

이제 고려해야 할 것은 무엇일까?

저항의 크기.. 트랜지스터의 W/L.. 테일 전류원의 현실..

차동 증폭기에 대해서 앞전에 설명했었던 이상적인 차동쌍은 저항의 크기, 트랜지스터의 사이즈가 동일했었다.

하지만 실제적인 회로에선 공정의 부정합(Mismatch)때문에 동일한 사이즈를 가지는 것이 힘들다.

추가적으로 테일 전류원을 이상적인 전류원으로 보았기 때문에 이상적인 전류원의 출력 저항을 무한대로 가졌는데 실제로 회로를 구현할 때는 MOSFET의 레벨로 설계하기 때문에 이상적인 전류원의 출력 저항은 무한대가 아니라 유한한 값을 가진 ro로 보아야한다.

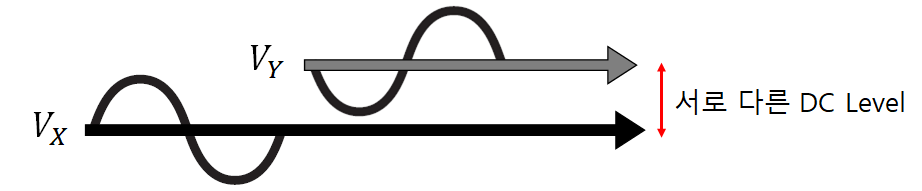

그럼 결과적으로 공통모드를 가진 출력 전압(Vxy)은 0이 아니게 된다. 다시 말해서 차동 쌍의 출력 전압은 서로 다른 직류의 레벨의 결과로 나오게 된다.

결과적으로 차동 증폭기 회로에서의 부정합(Mismatch)의 영향은

1. 노드 X와 Y에서의 서로 다른 직류 레벨로 인핸 공통모드 레벨(Common mode Level)의 변화

2. 공통모드 레벨의 변화는 차동 증폭기에서 다른 차동 성분을 유발하게 된다.

이 중요한 두가지를 아래 세가지 과정(유한한 출력 저항을 가지는 테일 전류원, 저항, 트랜지스터)을 살펴보도록 한다.

같은 저항의 크기, 같은 트랜지스터의 크기

유한한 출력저항을 가지는 테일 전류원

절반회로를 증명할 때 노드 P에서의 전압의 변화가 없기 때문에 가상접지로 만들 수 있었던 것을 생각해 봅시다

하지만 유한한 저항이 있게 되면 노드 P의 전압은 변화를 겪게 되고 결과적으로 0의 공통모드 이득에서 0보다 큰 공통모드의 이득을 가지게 됩니다.

어떻게 가지는지 알아보죠

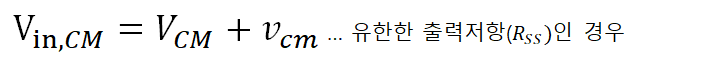

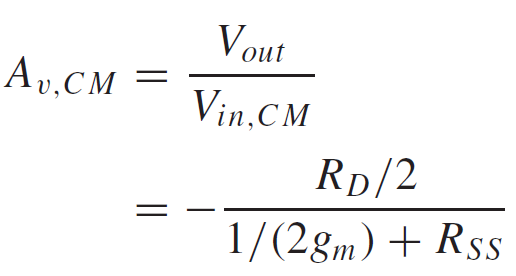

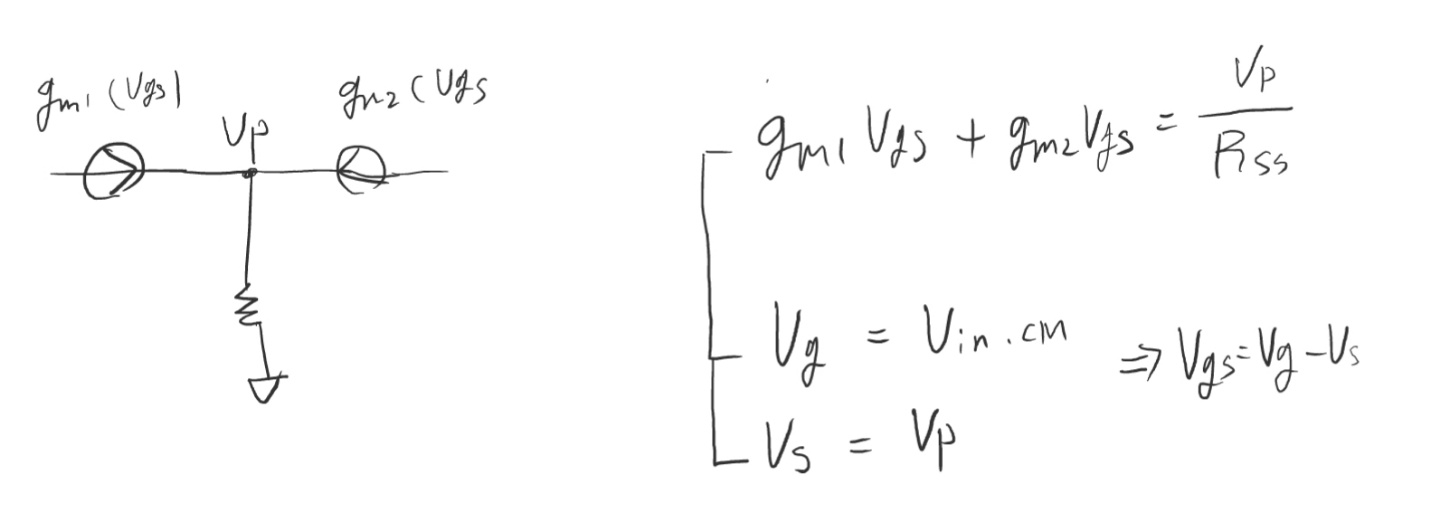

사진 1에서 공통모드 입력이 바이어스를 잡기위한 Vcm과 잡음성분 또는 간섭으로 인한 입력인 vcm이 들어온다고 생각을 해봅시다.

기존에 무한대의 전류원 출력저항은 개방회로가 되기 때문에 두 입력의 변화가 생겨도 노드 P에선 변화를 느끼지 못하게 되는 것을 절반 회로 증명에서 확인했습니다.

(두번째 진도인 절반회로해석 파트 참고)

KVL을 적용해 확인해 보면 아래와 같은 식을 알 수 있습니다.

vcm은 잡음으로 신호이며 시간에 따라 값이 변하게 되는데 이는 식 2와 같이 표현이 가능합니다.

식 2를 통해 알 수 있는 점은 노드 P의 전압도 변하게 된다는 사실을 알 수 있죠.

사진 1과 같이 Vin,CM으로 표현하기 위해 식 2를 식 3으로 바꾸어 표현해보면

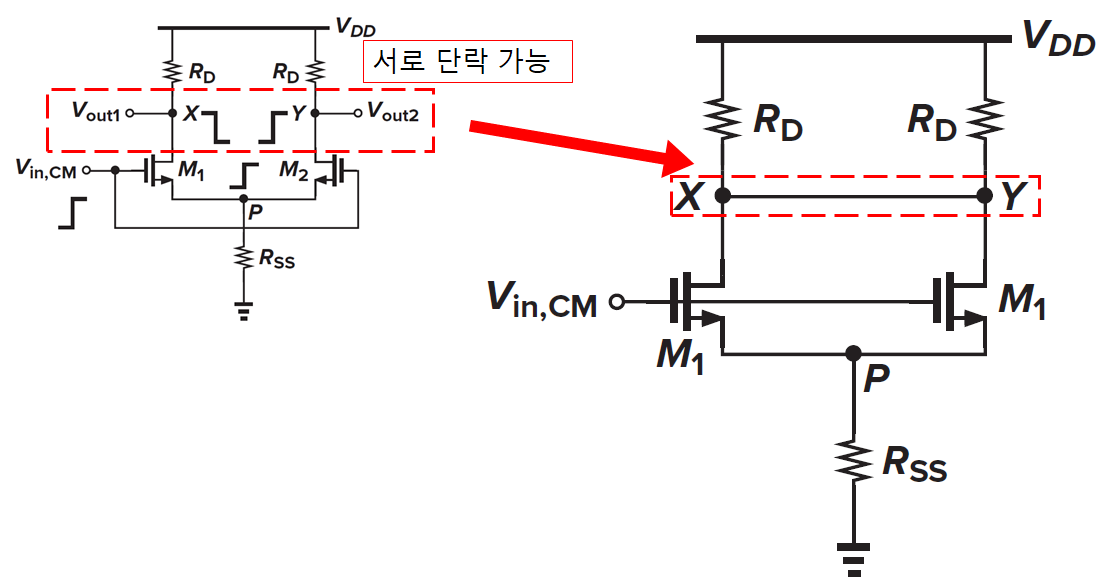

노드 P의 전압이 바뀌면 결국 Vout1,2도 같이 변함을 의미하고 이는 절반회로에서 두 전압의 변화가 같을 때 가상접지의 개념을 사용하여 Vout1,2의 단자가 서로 단락되어 연결이 됨을 알 수 있습니다.

결국 노드 X와 Y는 같은 노드가 되어 RD와 M1, M2 모두 병렬 연결이 되고 같은 크기를 가지게 되니 병렬 RD는 절반의 값, M1, M2의 Width(W)는 병렬연결 되어 2배의 W를 가지게 됩니다.

이에 대한 결과를 사진 3으로 표현이 가능한 것이죠

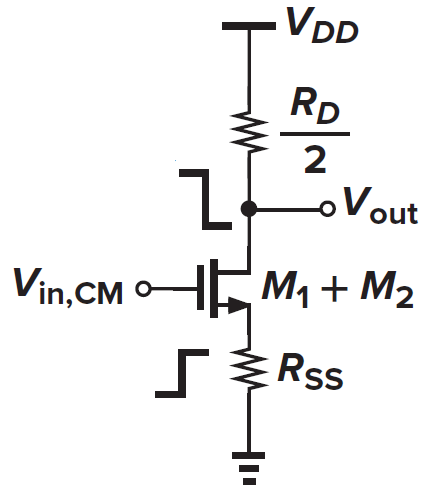

사진 3의 구조는 결국 축퇴 저항을 가진 공통 소스 증폭기가 되고, 공통모드 입력 중 하나인 vcm은 변하는 값이기 때문에 축퇴저항의 전압변화로 생기는 출력전압의 변화는 결국 소신호 해석과 동일하게 볼 수 있습니다.

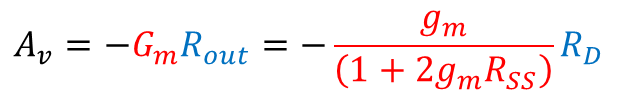

식 4를 정리하면 아래와 같으며 축퇴 저항을 가지는 공통 소스 증폭기에서의 표현 GmRout으로 표현은 각 색갈로 볼 수 있다.

식 5는 뒤에 나올 주제를 이해하는데에 도움이 된다.

정리해서 말하게 되면 원래는 0이였던 공통모드 전압이득은 유한한 테일 전류원의 출력저항과 어떤 잡음이나 간섭으로 인해 바이어스 점을 흔들게 되고 이는 소신호이득으로 변하게 된다.

다른 저항의 크기, 같은 트랜지스터의 크기

유한한 출력저항을 가지는 테일 전류원

꾸준히 언급을 했었지만 (트랜지스터도 마찬가지지만) 저항은 공정의 부정합으로 인해서 같은 값을 가지는 것이 아닌 서로 다른 저항값을 가지게 된다.

차동 증폭기에서의 서로다른 저항값의 의미는 결국 M1과 M2와 연결된 저항의 전압 강하의 크기는 서로 다름을 의미하게 된다.

(계산의 편의성을 위해 채널 길이 변조는 무시하지만) M1과 M2 드레인-소스의 전압(Vds)은 서로 다른 값을 가지게 되고 이는 Vout1과 Vout2의 DC 레벨의 높낮이가 서로 달라짐을 의미하게 되고, Vin,CM에 있는 잡음 및 간섭의 성분이 완전히 지워지지 않는 다는 것을 의미한다. 이해를 돕기 위해 사진 4를 참고하기 바란다.

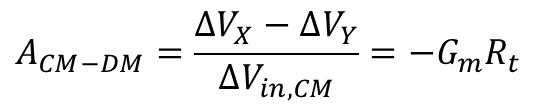

사진 5는 저항의 부정합이 있는 회로를 표현한 것이며 공통모드 입력은 위에서 언급했던 것과 동일하게 바이어스 성분과 잡음성분이 있다.

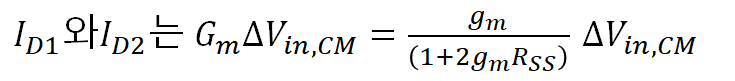

결국 델타 Vin,CM는 노드 P에서도 델타 Vp임으로 M1과 M2의 사이즈는 같기 때문에 둘이 병렬연결로 표현이 가능하며 트랜지스터의 전류의 변화는 아래와 같이 표현 가능하다.

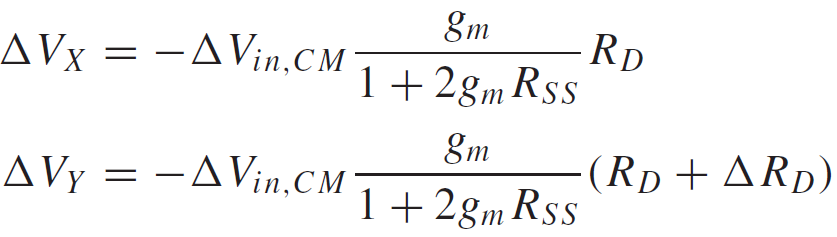

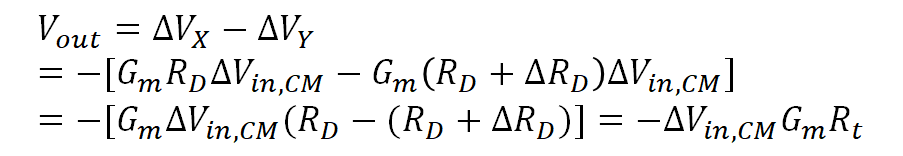

하지만 노드 X와 Y의 변화는 다르게 변화하기 때문에 이 두 노드의 변화의 표현은 아래와 같다.

서로 다른 저항성분으로 인해 DC레벨과 달라진 각 노드의 잡음 또는 간섭의 요동으로 증폭이된 공통모드 출력 스윙은 차동 성분을 유발함을 알 수 있다.

다시 말하면 입력에서의 공통모드 변화는 출력에서 차동 성분을 유발함을 의미한다.

따라서 이는 아래와 같이 표현 가능하다.

혼동을 위한 계산을 피하기 위해 Rt는 아래와 같다

식 10은 입력에서의 공통모드에서 차동모드로의 변환을 의미한다.

Gm은 식 5에서 표현 되었다.

이에 대한 결과는 사진 6에서 볼 수 있다.

같은 저항의 크기, 다른 트랜지스터의 크기

유한한 출력저항을 가지는 테일 전류원

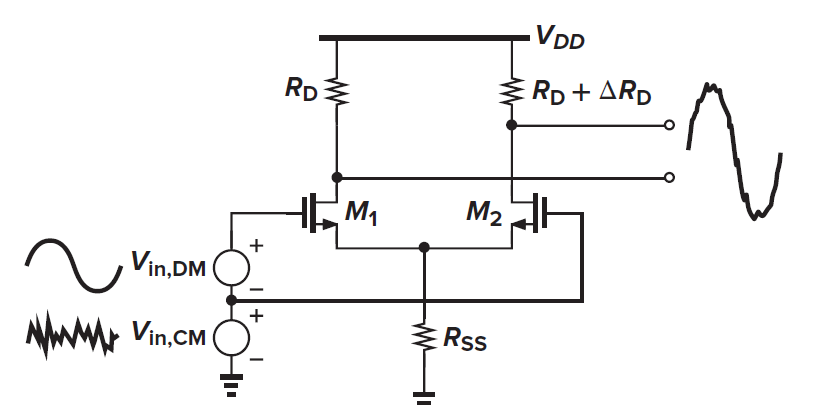

사진 7의 회로 표현은 서로 다른 트랜지스터의 크기 때문에 M1과 M2는 서로 다른 전류를 흘리고, 같지 않은 트랜스컨덕턴스를 가지게 된다.

왜 gm1, 2로 표현될까?

유한한 출력저항, 공통모드 입력에 잡음 성분 또는 간섭이 들어오면 공통모드 입력에도 소신호 성분이 들어오기때문에 M1과 M2의 소신호 성분을 구하기 위해서이다. 이해가 어렵다면 앞에 과정들을 다시 생각해보자

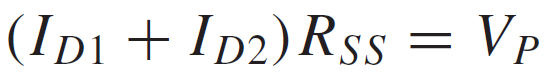

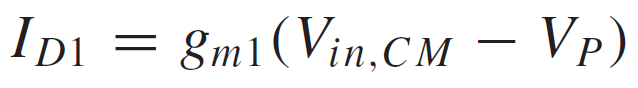

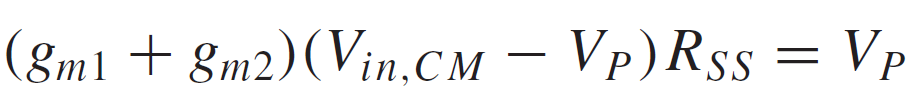

노드 P에서 M1, M2의 전류의 합이 유한한 출력저항 Rss에 흐르느는 전류가 되니 KCL을 통해 계산하면 아래와 같다.

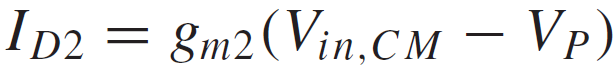

따라서 각 MOS에 있는 게이트 전압은 공통모드 입력이 들어오고, 소스 전압에는 노드 P의 전압임으로 드레인 전류는 아래와 같이 표현 가능 하다. 식 11 KCL의 결과값에서 우변에 있는 값은 노드 P에 흐르는 전류이다.

식 11에서 게이스-소스 전압을 표기하면 아래와 같다.

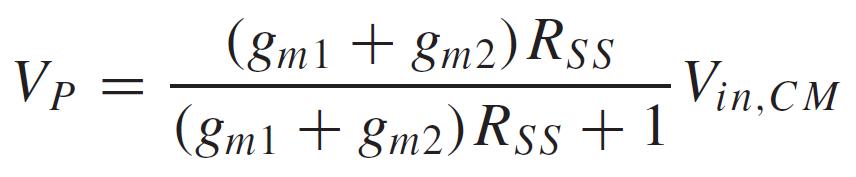

식 15에서 VP에 대한 값을 얻기 위해 식을 풀어서 쓰면 식 16이 된다.

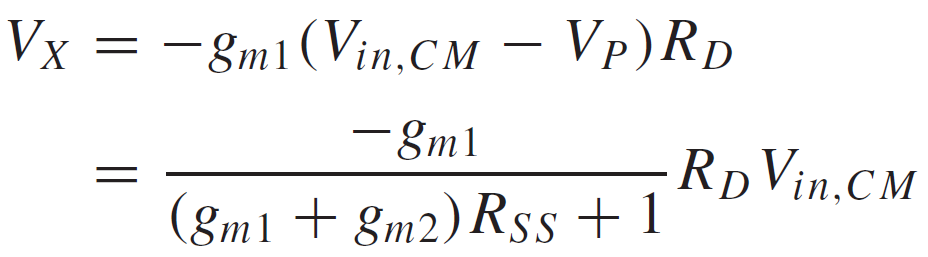

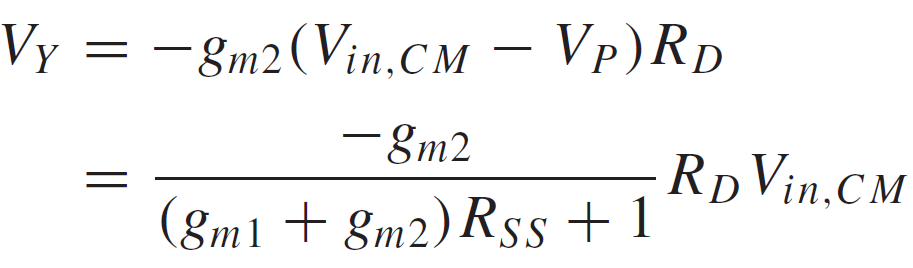

Vp 전압을 알았고 공통모드입력에서의 소신호 이득을 구하기 위해 사진 7에서 노드 x, y의 개별적인 전압이득은 아래와 같다.

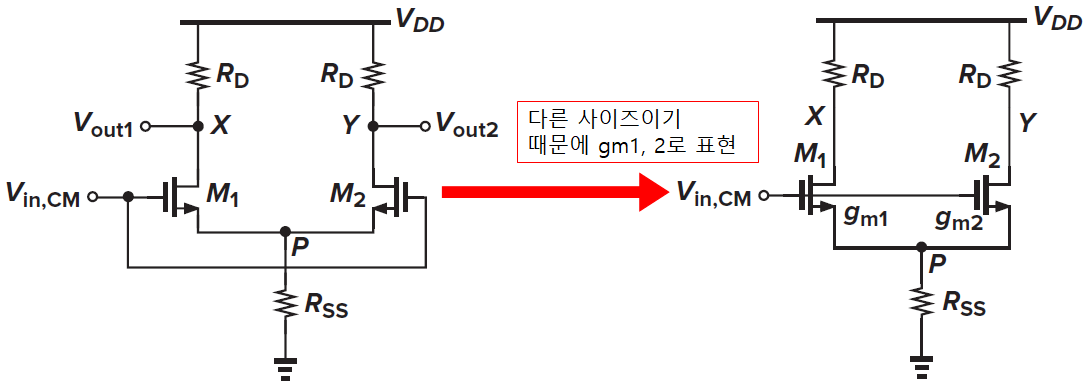

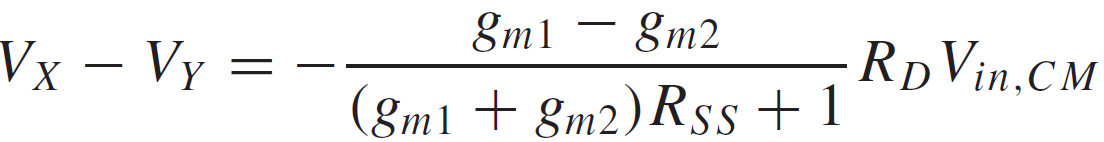

출력 전압 Vout=Vx-Vy 이므로 출력 전압을 구하게 되면 아래와 같다.

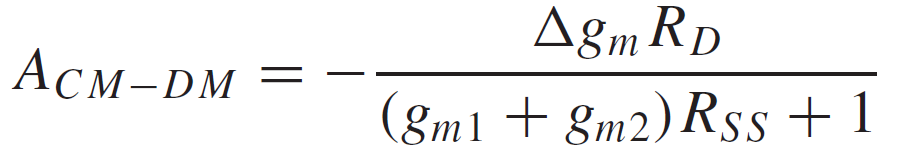

공통모드 입력의 변화는 차동성분을 유발함으로 이에 대한 공통모드에서 차동모드로 변환된 이득은 아래와 같다.

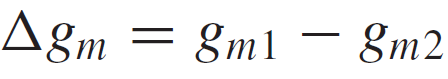

식 19에서 델타 gm은 아래와 같다.

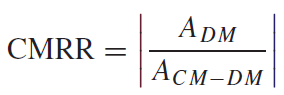

CMRR(Common Mode Rejection Ratio, 공통 모드 제거비)

여태 우리는 무엇을 한 것일까?

공정의 부정합이 없었던 차동 증폭기 회로의 공통모드 이득, 차동모드 이득을 먼저 배우고 유한한 테일 전류원의 출력저항, 각 소자의 부정합을 통해 0의 공통모드 이득에서 값이 존재하는 공통모드에서 차동모드로 변환하는 이득을 구했다.

항상 모든 회로는 설계자가 원하는 대로 이상적인 값을 구현할 수 없기 때문에 칩을 설계하는 사람들이 고려해야하는 파라미터인 CMRR을 알기 위해서 구한 것이다.

CMRR은 어떻게 구하는건데?

공통모드 변화에 의해 발생하는 원하지 않는 차동성분을 증폭의 결과를 원하는 차동 출력성분으로써 정규화를 하는 것이다. 이를 CMRR 즉 공통모드 제거비라 한다.

원하는 이득을 원치 않는 이득으로 나눈 값으로 정의된다.

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 트랜지스터의 과도 주파수(Transit Frequency) 차단 주파수? 이게 뭔데 (0) | 2021.10.22 |

|---|---|

| MOSFET의 커패시턴스 성분을 알아보자 (7) | 2021.10.22 |

| BJT의 NPN, PNP 동작과 얼리 효과(early effect) (0) | 2021.10.15 |

| 차동증폭기의 대신호와 소신호해석 (0) | 2021.10.15 |

| 단일 증폭기와 차동 증폭기의 차이점과 장단점 정리 (0) | 2021.10.13 |

댓글