개인 학습장입니다.

부족한 부분이 있다면 많은 지적바랍니다.

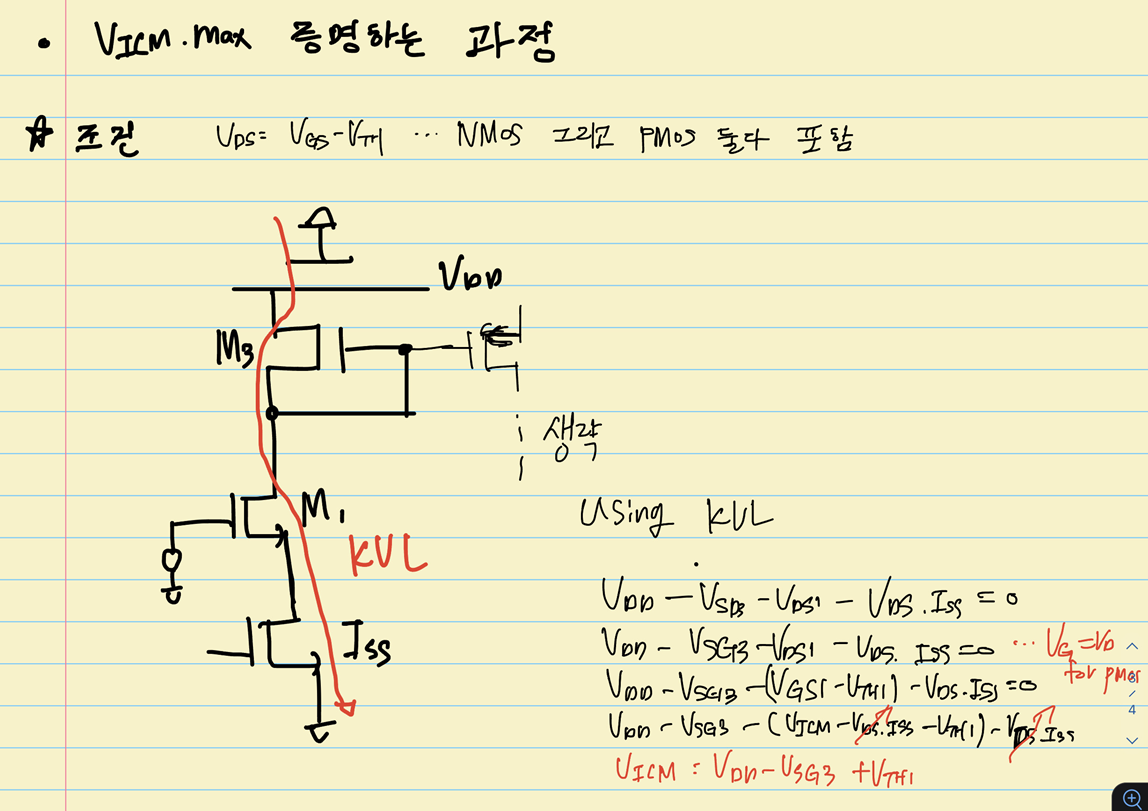

기본 토폴로지로 구성된 1단 연산증폭기

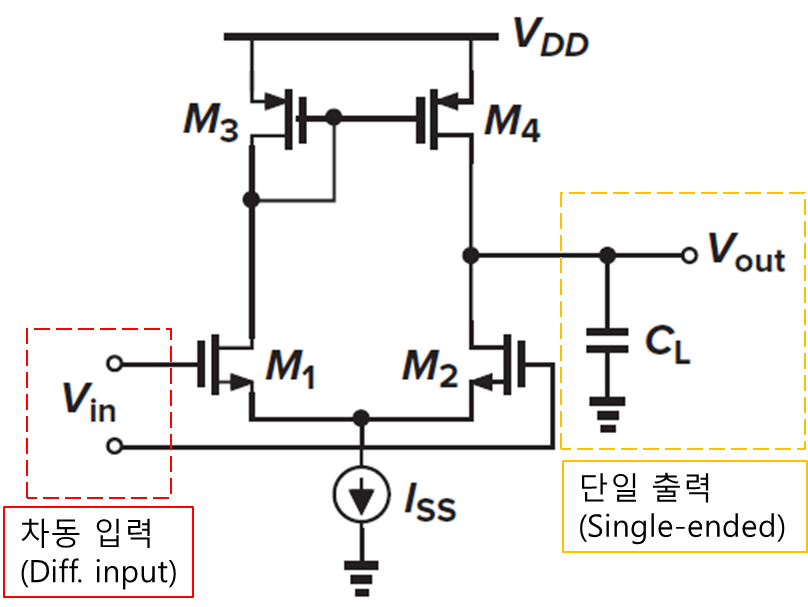

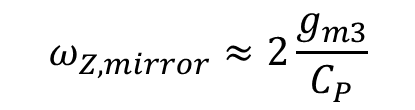

연산 증폭기는 차동(differential) 입력을 받아 단일(single) 출력을 나가는 differential input and single-ended op. amp가 있고 차동 입력을 받아 차동 출력으로 나가는 differential input and differential output op. amp가 있다. 해당 구조는 각각 전류 거울이 active load 역할을 하는 차동증폭기와 일반적인 차동 증폭기가 대표적인 예시이다. 아래 그림 1은 위에 언급한 구조들을 보여준다.

그림 1 구조들의 낮은 주파수 이득은 아래와 같다.

식 1을 통해 그림 1과 같은 기본 토폴로지로 구성된 OP amp는 서브마이크론 소자에서 20을 초과하기 어렵다. 다시말해 낮은 이득을 가지는 구조이다.

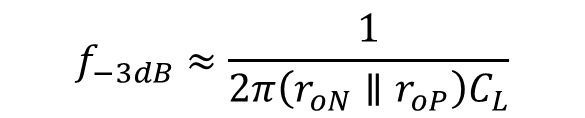

그리고 로딩 Cap이 있는 구조에서 주 극점(dominant pole)은 아래와 같다.

기본 토폴로지로 구성된 op amp

Type 1. 전류 거울 능동부하를 가진 1단 연산증폭기

1. 최소 입력 공통모드 전압(Minimum input common-mode voltage)

전류원(Iss)를 포화영역에 동작하기 위해서는 해당 MOS의 Vov와 Vds가 있을 것이고, M1,2를 동작시키기 위한 Vgs가 있을 것이다. 따라서

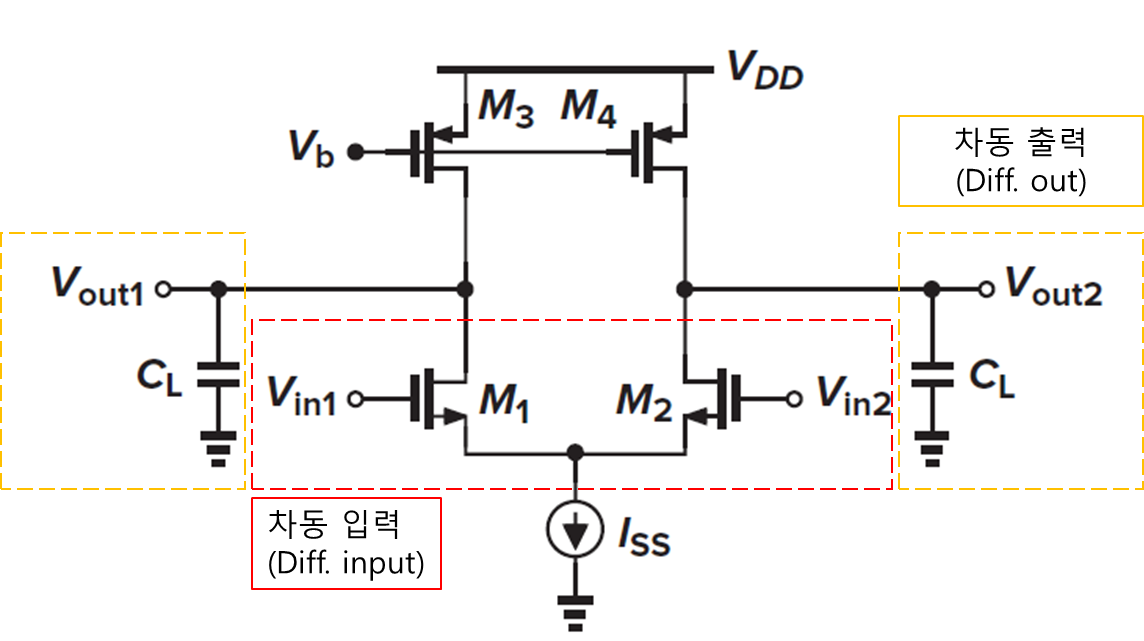

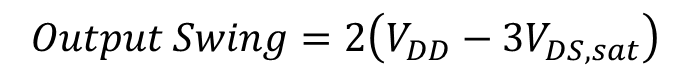

2. 최대 입력 공통모드 전압 (Maximum input common-mode voltage)

그림 1의 능동 부하를 Sat에서 동작시키기 위해 최대 입력 공통모드 전압은 아래와 같다.

식 3부터 4까지의 범위를 입력 공통모드 범위(Input common-mode range, ICMR)이라 부른다.

(식을 유도하기 위해서는 KVL이 적용된듯 하다. Vicm은 vgs로 생각하고 +vth는 좌항으로부터 이항된 것으로 보임)

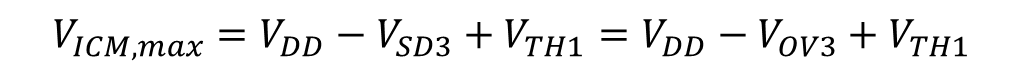

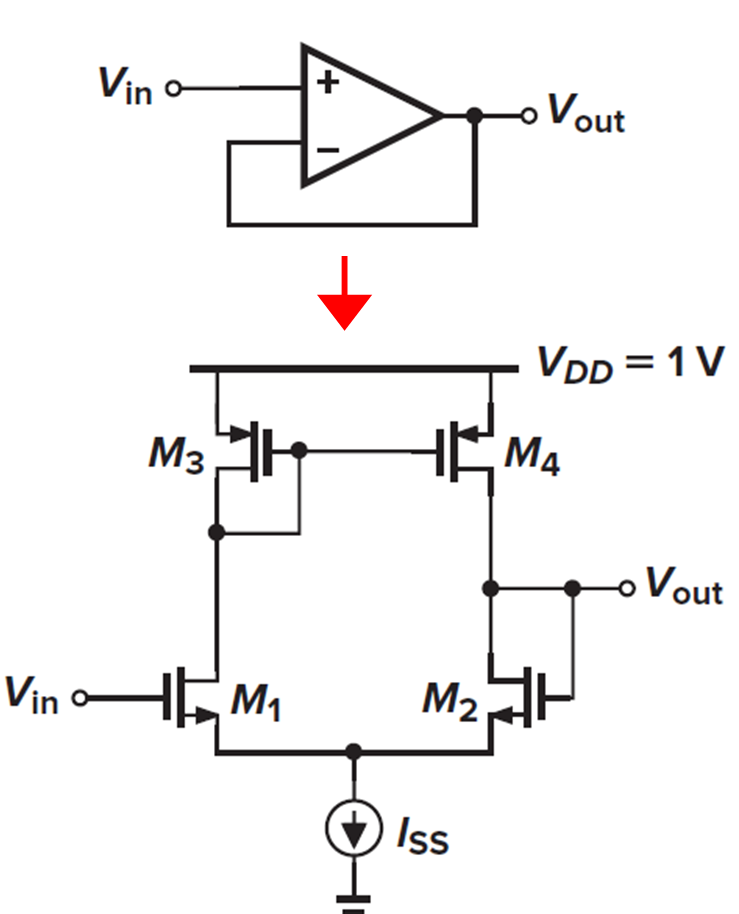

3. 출력 스윙 (Output swing)

출력 스윙은 M1,2 와 Iss 는 sat에 동작시키게 만들어야 함으로 2배의 Vds(=Vov) 전압이 필요하다.

Vdd부터 M4가 sat에서 동작시키기 위한 Vds(=Vov) 전압이 필요하다. 따라서 최대 출력 스윙은 Vdd-3Vds,sat이다.

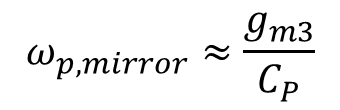

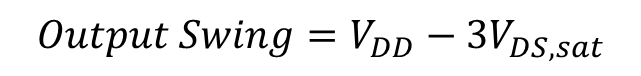

4. 단일 출력 회로의 미러 극점(Mirror pole)과 영점

그림 3을 통해 전류 거울에 의해 극점이 생기는데 이를 미러 극점이라고 한다.

Cp는 M1, M3, M4에 의한 기생 커패시턴스의 총합을 나타내고 저항성분은 M3를 바라보는 레지스턴스는 1/gm3이다.

그리고 극점은 아래와 같다.

그림 3의 영점은 아래와 같다.

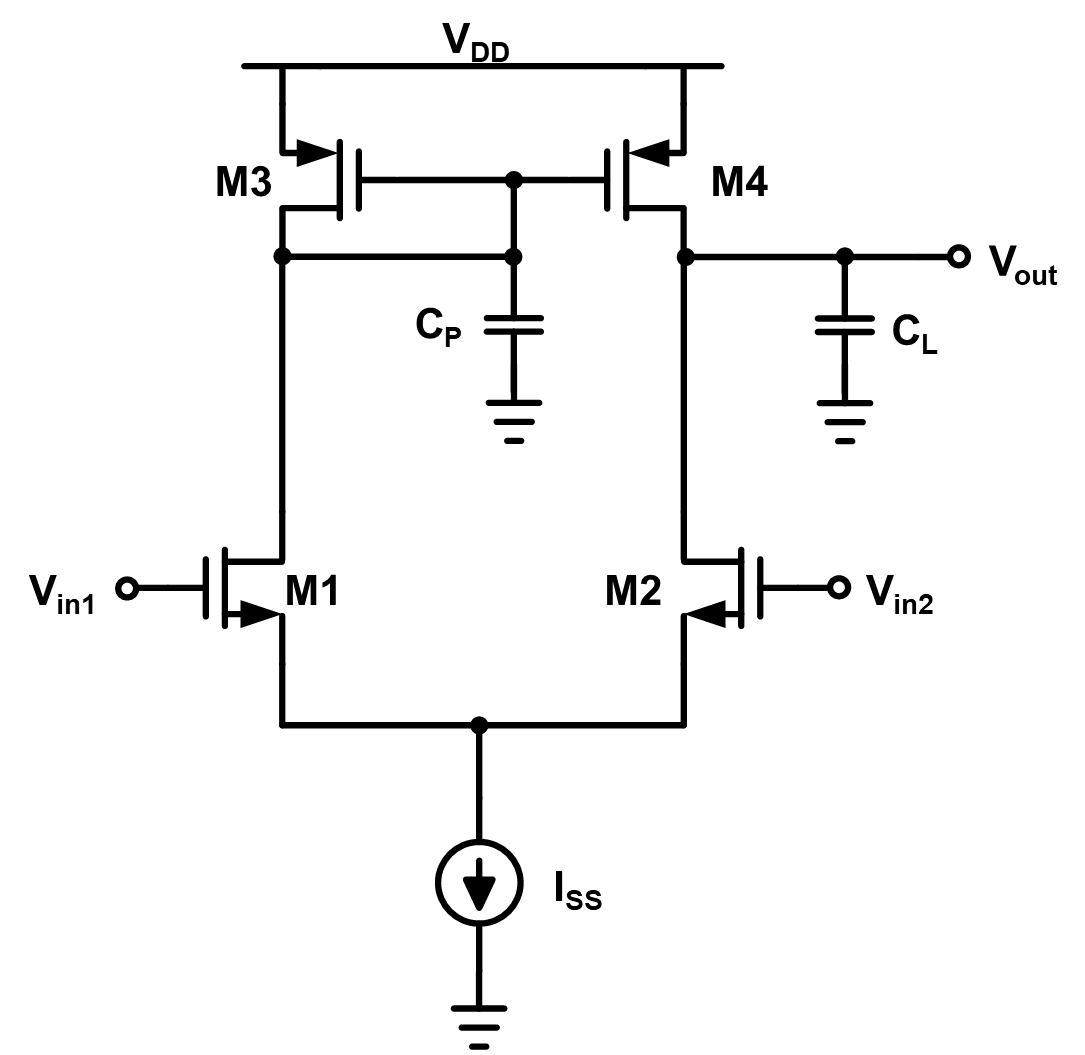

Type 2. 능동 부하로 구성된 op amp

1. 최소 입력 공통모드 전압(Minimum input common-mode voltage)

전류원(Iss)를 포화영역에 동작하기 위해서는 해당 MOS의 Vov와 Vds가 있을 것이고, M1,2를 동작시키기 위한 Vgs가 있을 것이다. (위에서 언급한 내용과 같다.) 따라서 최소 입력 공통모드 전압은 식 3과 같다.

2. 최대 입력 공통모드 전압 (Maximum input common-mode voltage)

그림 1의 능동 부하를 Sat에서 동작시키기 위해 최대 입력 공통모드 전압은 아래와 같다.

3. 출력 스윙 (Output swing)

출력 스윙은 그림 2와 같이

.

가진다 하지만 식 7은 one-side 출력이므로 해당 구조는 식 8과 같이 differential 출력으로 생각해야 한다.

4. 단일 출력 회로의 미러 극점(Mirror pole)과 영점은 없다.

전류 거울을 사용한 차동증폭기와 달리 해당 구조는 미러 극점이 없다.

로딩 캡으로 인한 주극점은 식 2에 언급했다.

Vicm,max를 증명하는 과정

PMOS Load를 가진 차동 증폭기도 동일한 과정으로 증명이 가능하다.

단위 이득 버퍼 (Unity Gain Buffer) 설계 예제

가정 : 문턱전압(Vth=0.3, Vov=0.1)

1. ICMR

식 3 ~ 4 에 대입하여 계산하면 0.5 < Vin <0.9 의 범위를 가진다 (Vgs-Vth=Vov)

2. Rout

피드백 챕터에서 폐루프 출력저항은 Rout/(1+KA) 이다. A=gmN(roN//roP) 임으로 출력 저항은 1/gmN 이 나오게 된다.

3. 폐루프 출력 극점

출력 극점은 ω=1/(RoutCL) 임으로 극점은 gmN/CL 에 위치한다.

잡음 해석

시간이 되면 작성하겠다.

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 능동 모드에서 동작하는 BJT에 대해 알아보자 (Active mode in BJT) (0) | 2023.03.16 |

|---|---|

| 마이크로 전자회로 3판 solution 통합 글 (12) | 2023.03.03 |

| 테브난 등가회로와 노턴 등가회로 (0) | 2023.01.27 |

| TYPE-Ⅱ(2) PLL에 대한 정리 (0) | 2022.07.25 |

| 기본 PLL(Phase-Locked Loop) 구조와 TYPE-1 PLL에 대해 (0) | 2022.07.24 |

댓글