이해를 돕기 위해 영상을 제작하여 올립니다. 아래 링크로 접속하여 보실 수 있습니다.

https://contents.premium.naver.com/informationgs/takeinformationgs/contents/230910145450903ss

[전자회로 2] 캐스코드 증폭기 (1)

해당 영상의 진도는 아래 링크의 진도에 대한 영상입니다. 필기 자료와 영상은 결제 후에 볼 수 있습니다. https://doctorinformationgs.tistory.com/138

contents.premium.naver.com

https://contents.premium.naver.com/informationgs/takeinformationgs/contents/230910151530005vn

[전자회로2] 캐스코드 증폭기 (2)

해당 영상의 진도는 아래 링크의 진도에 대한 영상입니다. 필기 자료와 영상은 결제 후에 볼 수 있습니다. https://doctorinformationgs.tistory.com/138

contents.premium.naver.com

(이어서 작성중)

캐스코드.. 너는 어떤 녀석이냐

BJT 회로에서는 공통 이미터(CE) 다음에 공통 베이스(CB)를 연결한 형태, MOSFET 회로에서는 공통 소스(CS), 공통 게이트(CG) 증폭기를 연결한 형태를 캐스코드 증폭기라고 부르게 됩니다.

왜 이런 캐스코드라는 구조를 쓰는지에 대해서는 입출력 저항과 전류 신호의 출력에 대해서 개별의 증폭기를 이해해야 합니다.

(편의상 MOSFET를 기준으로 설명하고, BJT는 부가적인 느낌으로 포스팅합니다)

먼저 공통 소스 증폭기(CS Amp)는 입력 저항이 크고, 출력저항이 입력 저항에 비해 작아서 전류 신호를 출력하기에 적합하고, 입력 저항이 상대적으로 낮은 공통 게이트 증폭기(CG amp)를 연결하여 전류 신호를 출력하기에 유용하면서 전압이득을 크게 출력할 수 있습니다.

캐스코드의 이해

캐스코드.. 에피타이저 소스 또는 이미터 축퇴(Source or Emitter Degeneration) 부터 살펴 보자

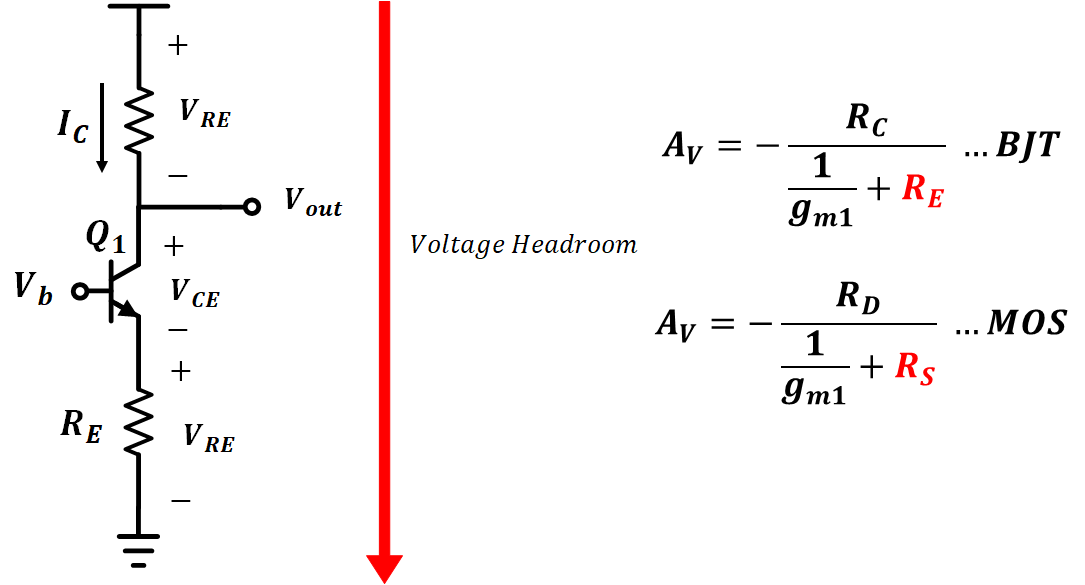

기존에 이미터 또는 소스 축퇴(Emitter or Source Degeneration)을 사용하면 출력저항이 Boost되는 것을 배웠다.

식 1을 보게 되면 이미터, 소스에 있는 축퇴 저항으로 인해서 출력 임피던스가 부스팅(boosting, 증가)되는 것을 알 수 있다. 하지만 두 가지의 문제점이 발생하기 되는데

1) 축퇴 저항의 전압 강하로 인한 공급 전압의 문제

축퇴 저항을 사용하게 되면 저항에 대한 전압 강하는 BJT나 MOSFET에 흐르는 전류의 세기에 따라 전압 강하의 양이 다르게 되는데 회로에 공급되는 전압 변화폭 즉 전압 헤드룸이 제한이 되게 됩니다.

2) 전압 이득의 감소

축퇴 저항을 사용함으로써 전압이득 분모에서 축퇴 저항의 값 만큼 더해주게 되며 이는 결국 전압이득이 감소하는 결과를 초래합니다.

따라서 이 두 문제를 해결하기 위해서 고안이 된 것이 바로 Cascode stage이다.

문제를 어떻게 해결했을까?

1) 공급 전압 헤드룸문제

전류의 양에 따라 축퇴 저항에 흐르는 전압 강하는 전류의 양에 따라 달라지기 때문에 해당 전압 헤드룸의 문제를 캐스코드에서는 트랜지스터를 쌓아(Stack)올렸기 때문에 해결 할 수 있다.

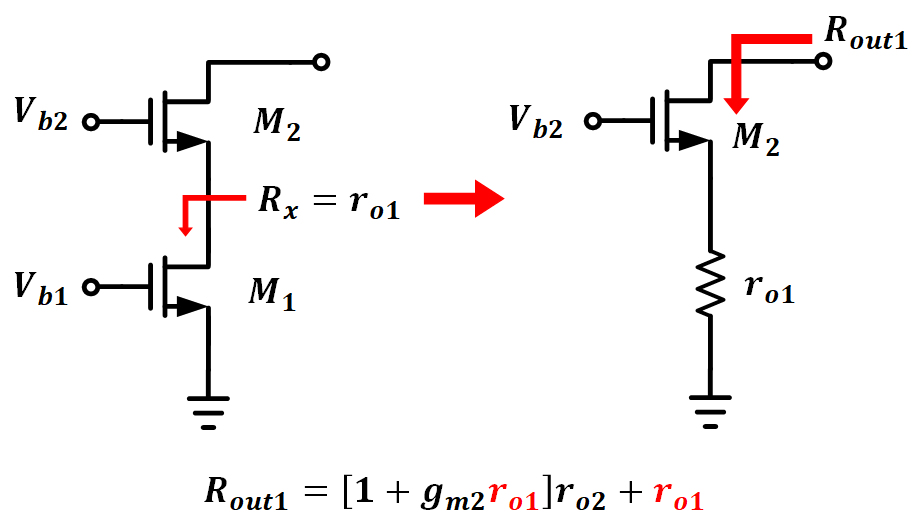

기존의 축퇴 저항을 가진 트랜지스터와 동일하게 출력 임피던스를 증가(Boost)시킬 수 있다.

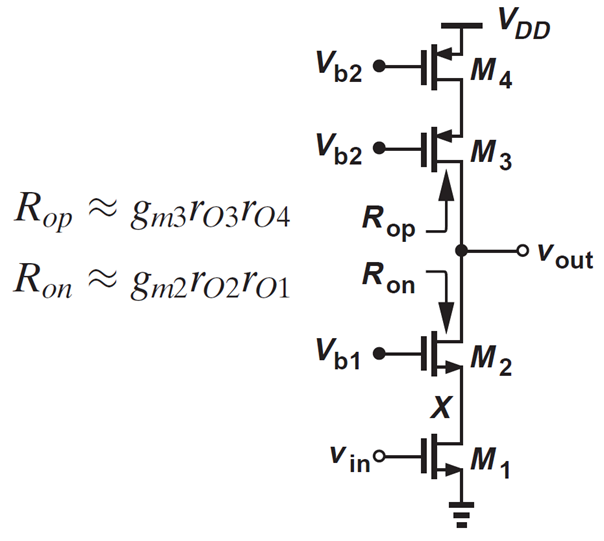

아직까지 캐스코드의 구조를 알지 못했지만 사진 3으로 캐스코드의 구조를 알 수 있다. 캐스코드 구조에서 M1은 동작하기 위한 DC 바이어스와 신호를 받는 ac 바이어스 두 가지를 입력으로 받는다.(Vb1 = VDC + vac)

출력 저항은 아래 식 1과 같이 근사할 수 있다

축퇴 저항을 가진 트랜지스터와 출력 임피던스는 비슷하나 차이점은 트랜지스터의 출력저항임을 기억하는 것이 좋다.

2) 전압 이득의 문제는 어떻게 해결했을까?

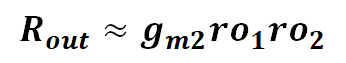

출력 저항이 무한대인 이상적인 전류원이 부하로 사용되고 Gm을 사용해 풀어쓰면 아래 사진 4와 같다.

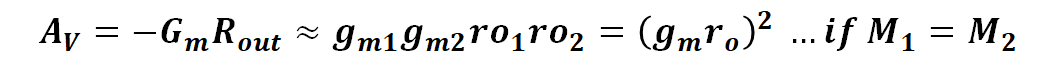

전압이득은 식 2로 표현 가능하다.

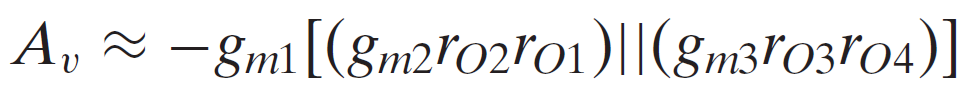

하지만 출력 저항이 무한대인 이상적인 전류원을 사용하는 경우는 불가능하기 때문에 부하에 PMOS를 위에 Stack 하는 구조를 사용하게 되는데 PMOS 하나만 올리게 되면 사진 2의 출력 저항과 PMOS ro의 병렬 저항은 ro가 더 작기 때문에 전압이득인 -gmro가 되어버리는 문제점이 생기게 된다.

따라서 M1과 M2와 사이즈가 동일한 PMOS 2개를 Stack 하여 조합한 캐스코드를 사용하면 출력 저항의 문제를 해결할 수 있다.

따라서 사진 5의 전압이득은 아래와 같이 표현 가능하다.

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 차동 증폭기 설계(Differential amplifier design) (0) | 2021.10.27 |

|---|---|

| 축퇴 저항 및 캐스코드 차동 증폭기 (0) | 2021.10.27 |

| Common Source Amplifier Design(공통 소스 증폭기 설계) (0) | 2021.10.25 |

| 공통 게이트(Common Gate, CG)에 대한 이론을 알아보자 (2) | 2021.10.23 |

| 소스 폴로워(Source Follower) 또는 공통 드레인(Common Drain,CD)에 대한 이론을 알아보자 (5) | 2021.10.23 |

댓글