반응형

캐스코드 차동 증폭기

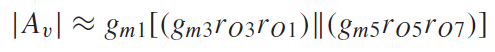

이전에 캐스코드에서 무한대의 출력 저항을 가진 전류원은 실제로 구현할 수 없고, PMOS로 구성된 부하의 값이 작으면 전압이득이 PMOS의 출력 저항을 따라가기 때문에(NMOS로 구성된 캐스코드의 출력저항이 높은 값을 가지고 있기 때문에 무시당함) PMOS를 2개로 Stack하여 올리는 것을 알고 있습니다.

완전하게 대칭인 회로인 경우 절반회로로 볼 수 있으며, 전압이득은 기존에 캐스코드에서 학습한 것과 동일하게 나옴을 알 수 있습니다.

축퇴형 차동 쌍

공통 소스 증폭기에서 축퇴 저항을 쓰게되면 제곱법칙 소자(MOS)의 선형성이 증가함을 볼 수 있는데 차동 증폭기에도 축퇴 저항을 넣어줌으로써 선형성을 증가시킬 수 있습니다.

동일한 사이즈를 가진 소자들로 가정하면 이도 절반회로로 해석이 가능하며 전압이득도 축퇴 저항을 가지는 공통 소스 증폭기와 동일함을 알 수 있다.

반응형

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 전류 거울(Current Mirror)의 원리를 알아보자 (4) | 2021.10.28 |

|---|---|

| 차동 증폭기 설계(Differential amplifier design) (0) | 2021.10.27 |

| 캐스코드 단(Cascode Stage)의 기본 (0) | 2021.10.25 |

| Common Source Amplifier Design(공통 소스 증폭기 설계) (0) | 2021.10.25 |

| 공통 게이트(Common Gate, CG)에 대한 이론을 알아보자 (2) | 2021.10.23 |

댓글