전류 거울은 집적회로를 설계할 때 아주 유용한 기법 중 하나이다.

왜 이런 기법이 유용한지에 대해서 알아보고, 하나하나 알아가 보면서 완벽히 이해해보도록 하기 전에 공정 변화(또는 변이, Process Variation)에 대해 알아야 한다.

Process Varition

| 종류 | 무엇과 연관이 되어 있을까 | 어떻게 되는데? |

| µ(이동도) | 온도 | 이동도가 달라지면 설계할 때 정한 드레인 전류의 변화 |

| Cox(게이트-산화막 커패시터) | 공정 | Cox가 달라지면 설계할 때 정한 드레인 전류의 변화 |

| Vth(문턱 전압) | 온도 | Vth가 달라지면 오버드라이브 전압의 변화로 인해 드레인 전류에 변화가 생김 |

| 저항(Resistor) | 공정 | 저항 바이어스회로를 구성할 때 저항 값이 달라지면 원하는 게이트-소스 전압(Vgs)을 인가하지 못하고 드레인 전류에 변화가 생김 |

저항 바이어스 회로가 가지는 문제점

저항이 가지는 부정합(Mismatch)

이상적으로 저항 바이어스 회로로 MOS에게 원하는 게이트 전압을 인가해주었더라면 얼마나 좋았을까?

하지만 실제 공정에서 저항을 제작할 때 발생하는 부정합으로 인해 저항은 내가 원하는 값이 안나올 수 있다.

자 여기서 R1, R2값이 바뀐다면 어떻게 될까?

Vgs의 값은 설계자가 원하는 값이 안나오기 때문에 당황할 수도 있다.

온도와 VDD의 변화 문제

MOSFET 물리를 자세히 배우게 되면 문턱전압 Vth는 온도의 영향을 받고, 게이트 전압은 VDD의 변화의 문제도 받게 된다. 여기서 VDD의 변화는 공급전압에 생기는 잡음으로 생각하면 이해가 빠를 것이다.

사진 1에서 언급된 Vgs의 전압은 VDD와 연관되어 있음을 확인해보자

식 1에서 알 수 있는 점은 변화하는 VDD는 드레인 전류의 변화를 일으키고, 온도의 변화는 문턱전압의 변화를 일으킴을 알 수 있게 된다.

운이 좋게도 "밴드갭 기준 회로"(Bandgap reference circuit)를 나중에 배우겠지만 이는 온도와 전압에 의존하지 않는 전압과 전류를 발생시키는 방법이 존재한다.

정리해보면

원하는 입력 전압과 전류를 만들고 싶지만 온도, 공급전압의 변화, 공정에서 발생하는 부정합으로 인해 원하는 값을 인가해주기 어렵다.

하지만 이런 문제점들을 어느정도 보완해주는 것이 전류 거울이다.

전류 거울의 원리

채널길이변조를 고려하지 않는 전류거울

채널길이 변조를 고려하지 않는 드레인 전류는 Vgs의 함수임을 알 수 있다.

자 어떤 기준 회로(REF, Reference)가 있고, 해당 기준 회로로 부터 복사되는 전류를 (Icopy) 만든다고 해보자 그리고 해당 회로는 MOSFET를 사용해 만들고 있음을 가정해보자

그리고 기준이 되는 드레인 전류(I_REF)는 어떤 기준 전압에 의해 만들어 지는 것을 알 수 있다.

복사되는 회로 전류도 어떤 입력 전압(게이트-소스)에 의해 전류가 만들어짐을 식 3을 통해 알 수 있다.

기준 전류를 만드는 회로로 부터 같은 전류를 만들기 위해서는 같은 전압이 인가되어야 하는데 이는 식2와 식 3이 같다고 생각하면 동일한 전류를 만들 수 있음을 알 수 있다.

식 4를 근거하여 MOS 전류 거울은 사진 3과 같이 만들어 질 수 있다.

사진 3은 M_REF의 드레인과 게이트의 전압은 같은 Vx이고 Vx는 M1에 입력됨을 알 수 있는데 이는 기준 전류(I_REF)양이 복사 전류(I_copy)와 동일하게 전류를 생성할 수 있다.

이는 식 5와 같이 설명이 가능하다.

기준 전류와 복사 전류에 대한 식은 식 6으로 표현할 수 있다.

식 5에 식 6을 대입하여 같은 공정상수(µ, Cox)와 오버드라이브 전압(Vx-Vth)은 상쇄할 수있다.

계산된 값을 정리하면 식 7과 같이 복사되는 전류(I_copy)는 복사되는 MOS의 (W/L)1과 기준 전류(REF)를 흐르게 하는 MOS의 (W/L)_REF의 비(ratio)에 따라 복사되는 전류의 양이 달라질 수 있음을 알 수 있고

(W/L)이 서로 같다면 복사되는 전류는 기준 전류와 동일한 전류의 양이 흐를 수 있음을 식 7로 부터 알 수 있다.

다른 의미로 식 7이 알려주는 건 무엇일까?

공정과 온도에 의존하는 µ, Cox, Vth가 없다는 것을 알 수 있다.

어떤 회로든 간에 기준 전류와 복사된 전류가 같은 양을 사용할 수 없고, 각각의 회로망에 따라서 설계자가 요구하는 전류가 있을 것이다.

식 7을 통해서 복사되는 전류의 비로 W나 L을 키우거나 줄이게 되면 원하는 양 만큼의 전류를 얻을 수 있으나, 문제점이 발생하게 된다.

해당 문제점을 알기 위해 동일한 기준 회로의 동일한 크기의 MOS를 직렬 병렬로 여러개를 사용하여 만드는 단위(Unit) 트랜지스터를 알아보도록 하자.

단위(Unit) 트랜지스터와 사이징 이슈(Sizing Issue)

복사 되는 전류를 N배로 키우고 싶을 때

식 7을 통해 복사되는 전류를 N배를 키우고 싶을 때 사진 3에 있는 회로에서 L은 고정시키고, M1의 W를 N*W_REF 만큼 키우게 된다면 기준 전류의 N배 복사 전류를 만들 수 있다.

하지만 단일 트랜지스터의 N*W_REF배로 키우게 되면 정확히 N*W_REF가 되지 않는다.

사진 4에서 보여주는 게이트 코너(Gate Corner)가 정확하게 정의 되지 않으므로 실제로 N배의 전류를 만들어 줄 수 없기 때문이다.

따라서 기준 전류를 만들어주는 M_REF와 동일한 사이즈를 N개의 MOSFET를 병렬 연결하면 게이트 코너가 M_REF와 비슷하게 맞출 수 있기 때문에 오차를 많이 줄여줄 수 있다.

그에 대한 예시는 사진 5로 표현되어 있다.

복사되는 전류를 1/N배로 만들고 싶을 때

식 7에서 알 수 있듯이 1/N배 만큼 기준 전류를 줄이고 싶을 때는 L을 키우면 된다. W를 키울 때와 마찬가지로 L을 키우면 소스 및 드레인 면적에 측면 확산에 의한 오차(L_D)를 최소화 하기 위해 대개 모든 트랜지스터가 W_REF와 동일한 방법으로 똑같은 길이를 가져야만 한다.

이해가 어려울 수도 있으니 아래 MOSFET 물리로 돌아가 L_D 부터 알아보자

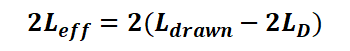

1/N배 만큼 만들고 싶다는 것은 Leff를 2Leff로 만든다는 것을 의미한다. L_D는 공정 과정을 통해 확산에 의한 것이기 때문에 M_REF의 Leff를 2Leff를 제작했다 하더라도 -4L_D를 만들 수 없다는 것이다.

따라서 이를 해결하기 위해 M_REF와 동일한 사이즈를 직렬로 연결하여

를 만들어 줄 수 있다.

그에 대한 예시는 사진 7로 표현 가능하다.

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 공통 소스, 소스 폴로워, 공통 게이트의 주파수 응답(Frequency response of Common Source, Gate and Source Follower) (3) | 2021.11.23 |

|---|---|

| 캐스코드 전류 거울(Cascode Current Mirror) (2) | 2021.11.04 |

| 차동 증폭기 설계(Differential amplifier design) (0) | 2021.10.27 |

| 축퇴 저항 및 캐스코드 차동 증폭기 (0) | 2021.10.27 |

| 캐스코드 단(Cascode Stage)의 기본 (0) | 2021.10.25 |

댓글