이 글은 학부 4학년 또는 대학원 진도임으로 다소 어려울 수 있음

기존에 전자회로에서는 채널 길이 변조(Channel Length Modulation)을 고려하지 않고 설계를 하였으나 드레인 전류는 Vgs와 Vds의 함수이기 때문에 결국 드레인-소스 전압의 영향을 받을 수 밖에 없게 되기 때문이다.

이 글을 읽기 전에 이전에 포스팅을 반드시 읽어주시기 바랍니다.

2021.10.28 - [전공(Major)/전자회로와 아날로그 회로설계] - 전류 거울(Current Mirror)의 원리를 알아보자

전류 거울(Current Mirror)의 원리를 알아보자

전류 거울은 집적회로를 설계할 때 아주 유용한 기법 중 하나이다. 왜 이런 기법이 유용한지에 대해서 알아보고, 하나하나 알아가 보면서 완벽히 이해해보도록 하기 전에 공정 변화(또는 변이, P

doctorinformationgs.tistory.com

전류 거울 이해의 핵심은 대신호 해석이다

해당 챕터를 이해하기 위해서는 각 단자간의 전압차이를 이해하는 것과 KVL을 통한 해석이 매우 중요하다.

그것만 이해하고 책에서 설명하는 수식들을 쉽게 이해할 수 있으며 스스로 바이어스를 맞추기 위한 회로들과 캐스코드 전류 거울을 붙여서 이해하는 것이 제일 좋은 방법이라 생각한다.(사람마다 다를 수 있음)

Vgs, Vds, Vgd 는 무엇을 의미하는 건지 알아야 한다.

전압에 표기된 아랫첨자는 전압차를 설명하는 것이다.

예를 들어

Vgs는 게이트-소스의 전압차를 이야기하는 것이며 통상 source 단자는 그라운드에 연결되어있기 때문에 0이고 Vgs를 해석하자면, Vgs=Vg-Vs=Vg-0=Vg이다.

Vds도 또한 Vd-Vs=Vd가 된다.

하지만 이번 전류 거울 파트에서는 Source 단자가 그라운드에 연결되지 않고, 어떤 전압을 갖게 됨으로 소스 단자의 전압이 존재함을 알고 넘어가자.

Vgd는 게이트-드레인의 전압차를 이야기하며 드레인 단자는 음의 부호를 가지는 것을 상기하는 것이 좋다(Vgd=Vg-Vd)

채널길이 변조를 고려한 전류미러

채널 길이 변조를 고려한 전류미러의 전류 복사 식은 아래 식 1과 같다.

식 1을 통해 알 수 있는점은 각각의 Vds1과 Vds2의 값이 같아야 (W/L)의 비로 전류를 복사가 가능하지만 값이 달라지게 되면 (W/L)의 비로 복사가 가능한 전류 복사식을 적용할 수 없다.

그러면 채널 길이 변조를 고려하게되면 어떤 문제점들을 가져오게 될까?

드레인 전류의 변화는 어떤 문제를 가져올까?

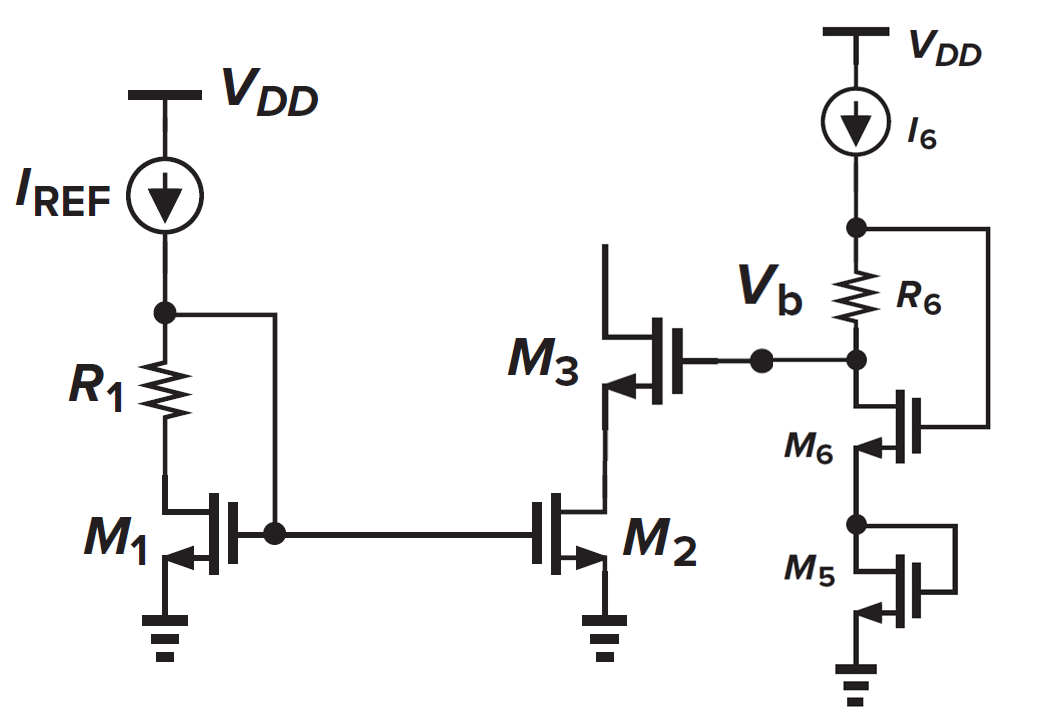

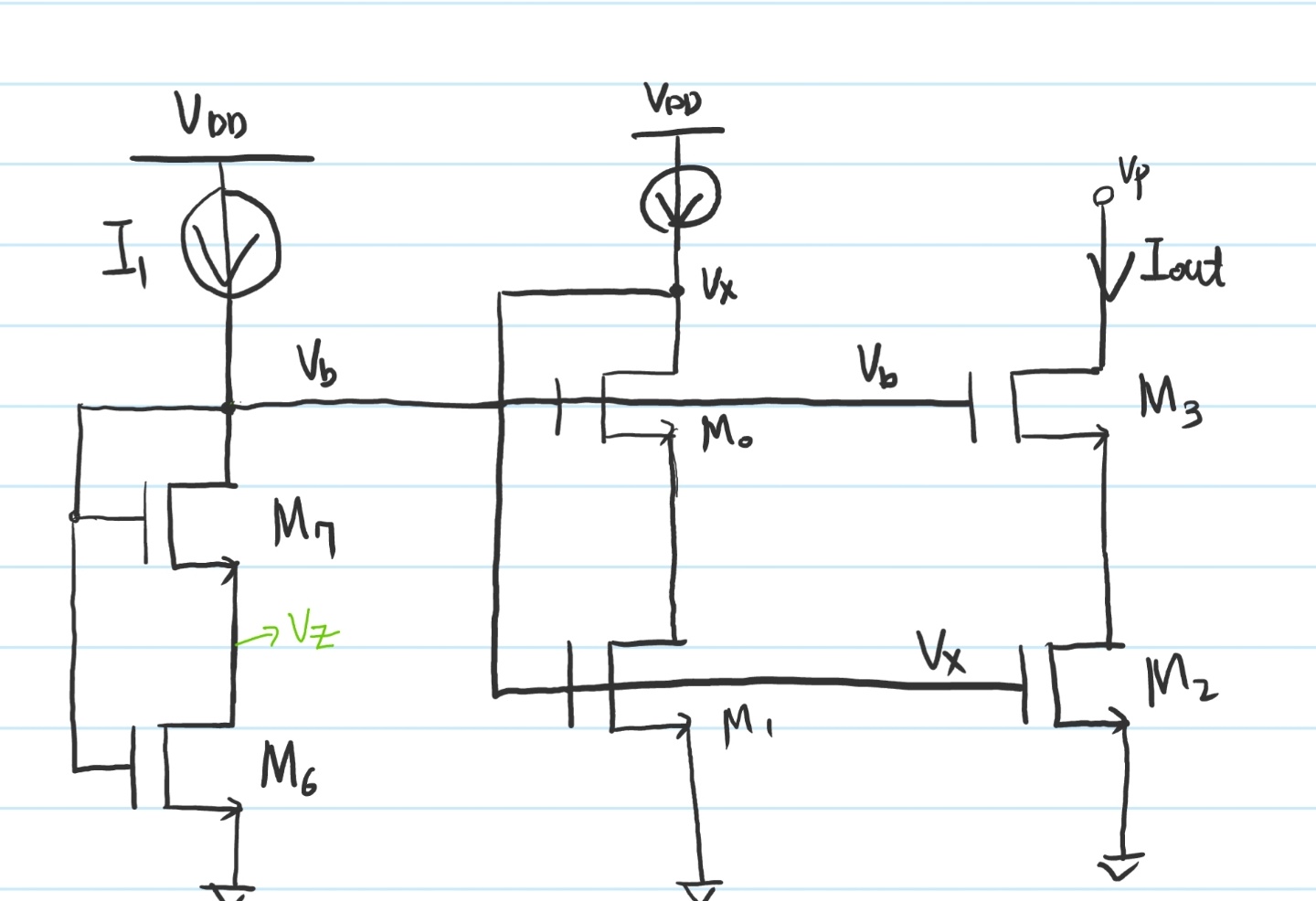

이전 포스팅에서 복사 전류를 만드는 M1이 사진 1처럼 드레인-소스 전압이 잡음 성분에 의해 변한다고 생각해보자

식 1을 사진 1과 같은 회로로 대입하여 풀데 되면 복사 전류는 흔들리는 양 만큼 복사 전류도 흔들리게 된다. 이를 의미하는 것은 이전에 채널 길이 변조를 고려하지 않았을 때는 Vy의 값이 흔들려도 전류는 그대로 복사가 가능했지만 지금은 아니라는 것을 의미하게 되고 일정한 전류를 공급하지 못한다는 문제점을 야기한다는 것이다.

(또는 REF의 드레인, 게이트 전압이 흔들려도 결국 복사식은 W/L의 비로만 복사가 가능했었다.)

이런 문제점을 이런 잡음성분에 관해 어느정도 막아주는 것 즉 차폐특성(Shielding property)을 가지는 캐스코드 구조의 전류 거울이다.

캐스코드 전류 거울

캐스코드의 차폐 특성

사실 캐스코드의 차폐특성은 소스 축퇴 저항을 가지는 CS 증폭기의 원리와 상당히 유사하다.

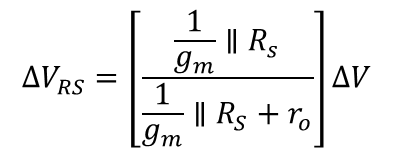

저항 Rs의 전압의 변화를 유심히 봐야 하는데 이 변화의 양은 ro의 값이 상당히 크기 때문에 작게 나온다. 이는 식 3을 통해 알 수 있다.

캐스코드는 식 3에서 Rs가 ro로 바뀌게 되는 것이 전부이다. 이는 식 4와 사진 3으로 표현 할 수 있다.

여태까지 채널 길이 변조를 고려하였고, 사진 1에서 복사 전류를 생성하는 M1의 드레인 전압의 변화 때문에 캐스코드 구조의 차폐특성을 사용하여 드레인 전압의 변화를 어느정도 해결하였고, 식 1, 2를 통해 Vds1과 Vds2를 같은 값으로 맞춰 줄 수 있다면 MOSFET의 사이즈인 W/L의 비로만 고려하여 복사 전류를 보다 쉽게 만들 수 있다.

Vds2를 Vds1에 같게 하거나 Vds1을 Vds2와 같게 만드는 두가지 기법이 있다.

(첫번째 기법) 목표 : Vds2가 일정하면서 Vds1과 동일하게 설계

사진 3에서는 캐스코드 전류원이 어떤 잡음 전압 특성에 대해 Vds2의 전압의 변화는 적다는 것을 보여주는 그림과 Vds를 갖게 하기 위한 목표를 보여주고 있다.

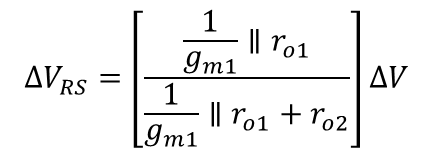

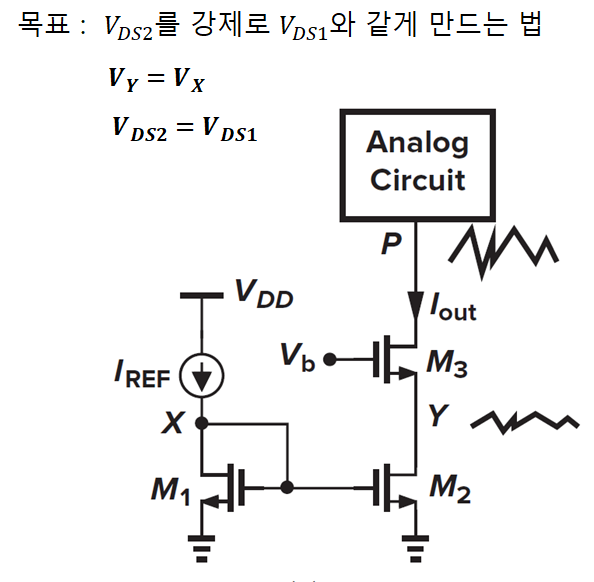

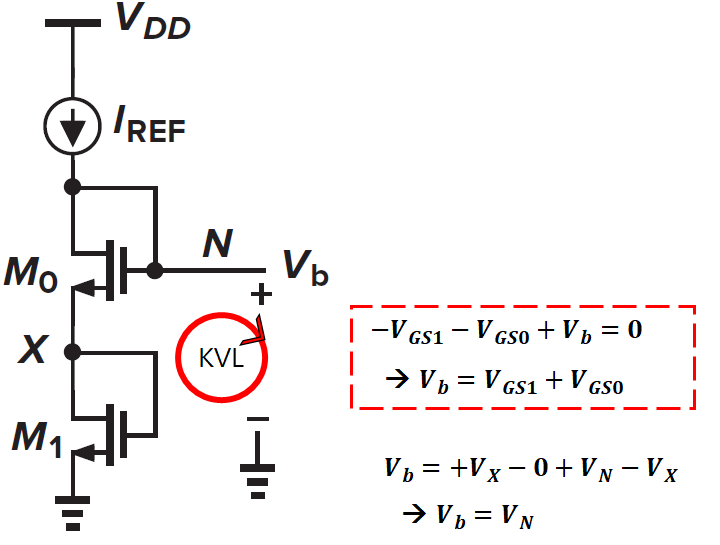

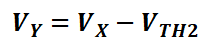

자 Vds2를 강제로 Vds1과 같게 하기 위해 아래 사진 4처럼 KVL을 돌려본다.

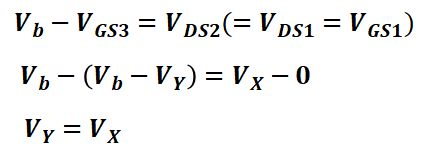

식 5를 통해 Vds2를 Vds1과 같게 하려면 M1의 드레인 전압과 같아야됨을 의미한다. 따라서 Vds2=Vds1=Vgs1=Vx를 의미하는 것이다.

식 5를 좀 더 자세히 풀어써보자 M3의 게이트 전압은 Vb, M3의 소스 전압이자 M2의 드레인 전압은 Vy이다. 식 5를 다시 풀어쓰면 아래와 같다.

식 6은 결국 사진 4의 목표와 동일함을 알 수 있고 식 6을 통해 Vb의 전압이 Vgs3+Vds1의 전압을 발생 시켜줘야 Vy=Vx가 되는 것을 보여준다.

그러면 Vb는 어떻게 발생 시키는가?로 설계 의문점에 직면하게 된다

이 의문점은 두 개의 다이오드 구조의 소자를 직렬로 연결하여 Vb를 생성함으로써 해결할 수 있다.

아래 구조를 보자

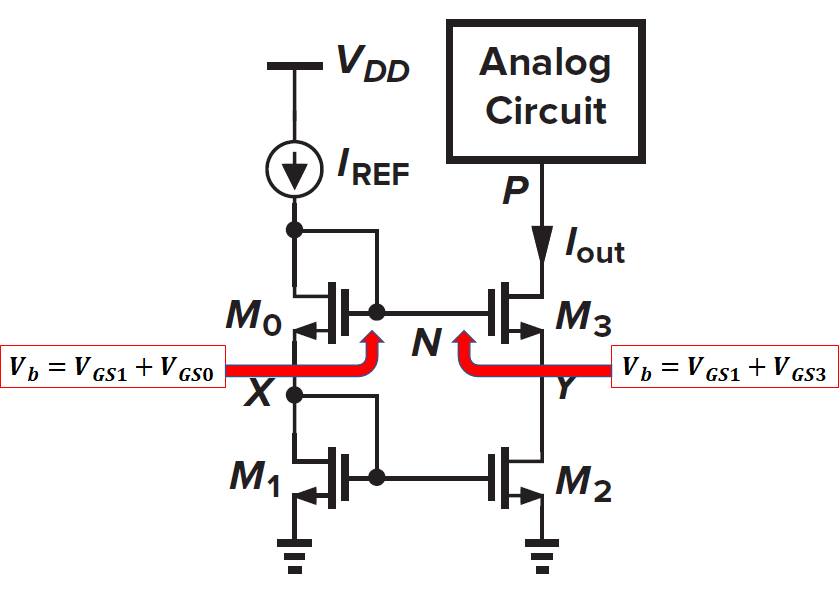

사진 5에 있는 M1위에 다이오드 구조의 M1을 연결하고 M0의 게이트는 Vb를 생성한다.

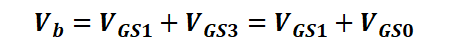

식 5를 참고하여, Vgs0=Vgs3와 동일한 값을 가지기 때문에 동일한 Vb를 생성할 수 있다.

이는 식 8로 조금만 계산해보아도 알 수 있다.

식 8의 Vgs1의 전압은 Vx와 Vy의 전압이며 이는 드레인 전압임을 명심하라

사진 6의 캐스코드 전류원은 캐스코드의 특성 중 하나인 높은 출력 임피던스를 가지고 정밀한 값을 가지는 전류원으로 동작하게 된다. 장점이 있으면 단점도 있는법이니 이제 단점을 알아보자

첫번째 기법 설계는 높은 전압 헤드룸을 가지는 단점을 가진다.

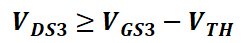

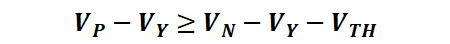

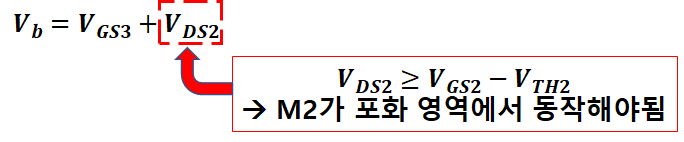

M3가 포화 영역에서 동작하려면 아래의 식이 성립되어야 한다.

각 노드의 전압으로 바꾸고 각각의 전압 차이로 설명하게 되면 아래와 같다.

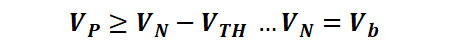

식 10의 Vy은 상쇄가 가능하므로 상쇄시키고 Vn전압이 Vb가 동일함을 식 7에서 알 수 있음으로

노드 P에서 허용 가능한 최소 전압은 아래와 같이 표현 가능하기 때문에 식 11에 식 8이 같다고 표현하면 아래와 같다.

식 12와 동일한 결과를 가지면서 오버드라이브 전압으로 표현하게 되면 식 12는 다음과 같이 수정할 수 있다.

이는 식 9처럼 포화 영역에 동작을 하려면 노드 P의 전압은 두개의 오버드라이브 전압과 한개의 문턱전압의 합과 같은데 이 결과는 많은 전압 헤드룸이 소모된다는 의미이다.

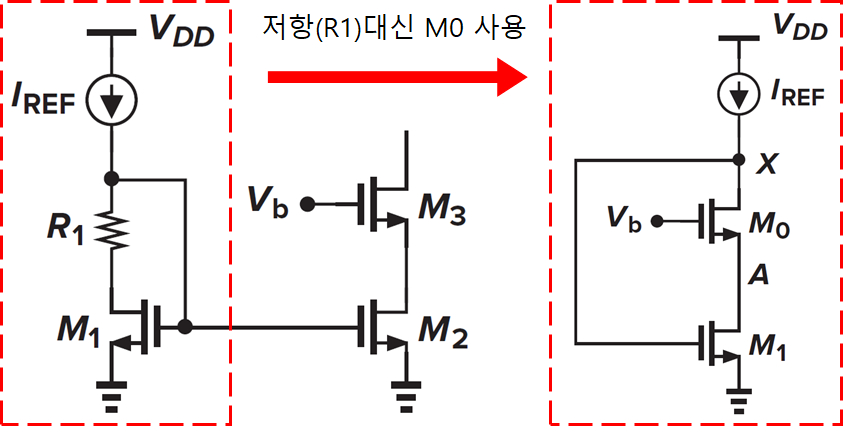

그래서 새로운 방법인 두번째 기법에선 전압 헤드룸에서 Vth의 불이익을 피하기 위해 Vds1을 강제로 Vds2와 같도록 만든다.

(두번째 기법) 목표 : Vds1이 일정하면서 Vds2와 동일하게 설계

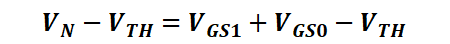

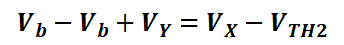

사진 4와 식 5로 돌아가보자 식 5에서는 M3에서 인가되는 전압이 M2를 포화영역에 동작하도록 전압을 인가를 해주어야 함을 내포하고 있다. 이에 대해 자세히 유도를 해보자면

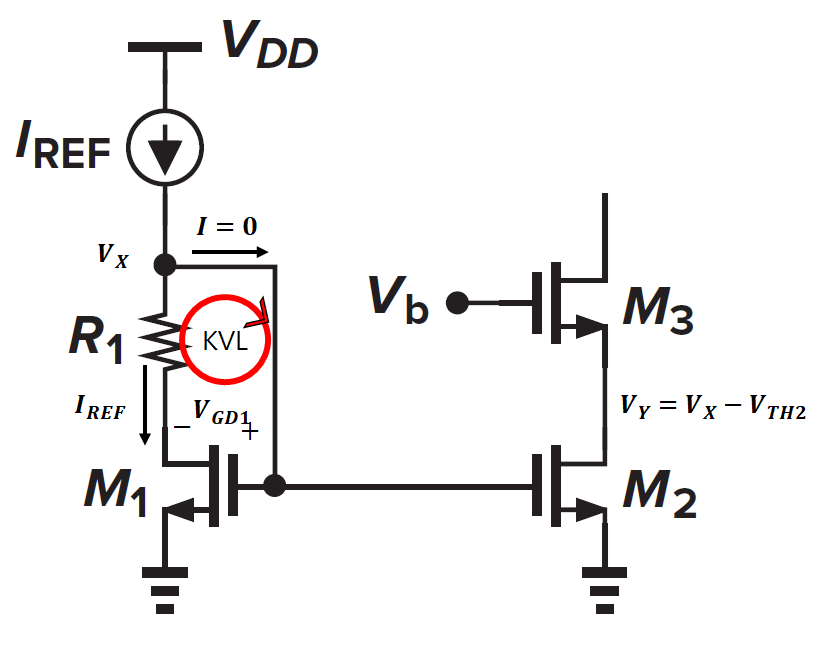

이를 Vds2를 동작시키기 위한 최소 허용전압은 Vds2=Vgs2-Vth2가 된다. 식 14를 정리해 보면

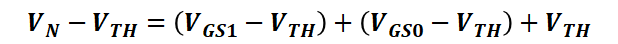

각 노드에 대해 표기를 하고 전압 차에 대해 계산을 해보면 아래와 같다.

식 16을 풀어서 나온 결과는 M2의 드레인 전압은 M2의 오버드라이브 전압이 나오게 된다.

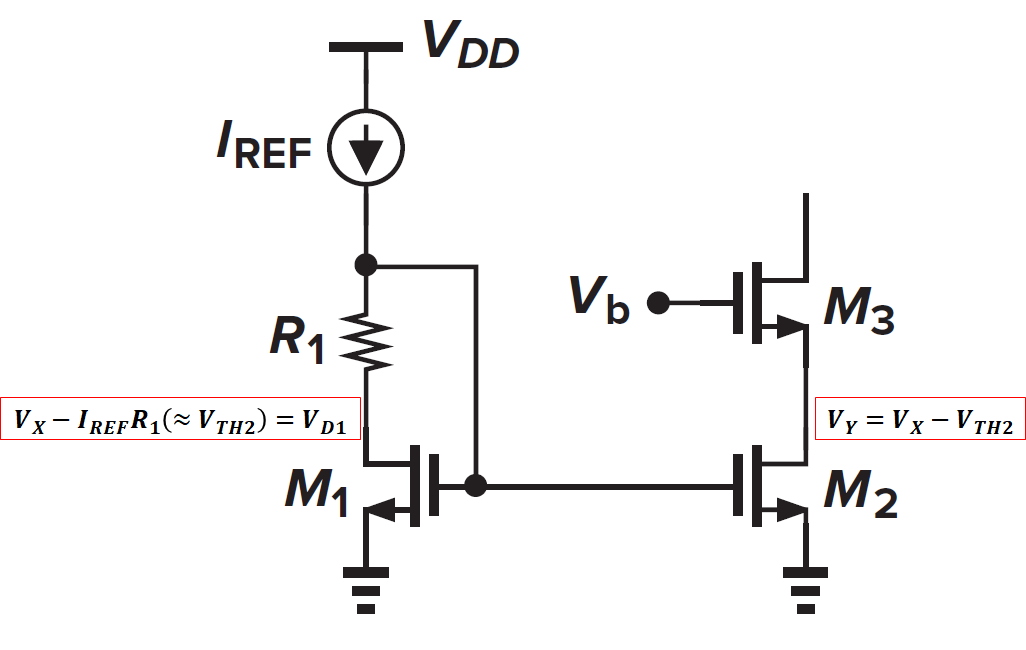

두번째 기법은 Vds1을 강제로 Vds2로 맞추는 것이기 때문에 M1의 드레인 전압도 식 17과 동일한 형태로 나와야만 한다. 이는 M1의 드레인 단자에 저항을 연결해 Vth2만큼의 전압 강하를 만들어주게 되면 식 17과 동일하게 맞출 수 있다.

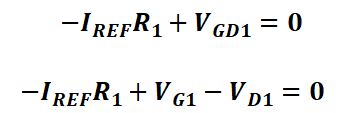

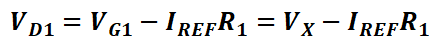

사진 7을 통해 폐루프에 KVL을 적용하여 계산하면 아래와 같다.

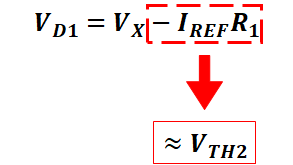

식을 다시 정리해보면 아래와 같다.

여기서 저항에 생기는 전압강하를 Vth2와 같게 설정한다면 식 17와 동일한 값을 맞춰줄 수 있다.

다시 정리하게 되면 아래와 같다.

하지만 사진 8을 통해 알 수 있는 점은 무엇일까?

첫째로 M2의 드레인-소스 전압(Vds2)은 Vds1이 강제로 맞춰주었기 때문에 결국 Vds1과 동일한게 표현이 가능하게 되며 식 17을 만들어 주는 것(Vb를 만들어 주는 것)이 만만치 않은 문제점을 가지게 된다.

두번째는 그놈의 PVT...변이(Variation)를 통해 R1과 문턱전압이 바뀌게 된다.

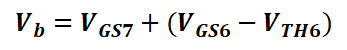

첫번째 만들어보자.. Vb 생성 회로(Vb=Vgs3+Vgs1-Iref)

사진 9에서 Vb 생성 회로는 식 18 ~ 20까지의 동일한 과정으로 Vb를 만들어 줄 수 있다.

Vb를 생성하기 위해 사진 9와 같은 회로를 만들어야 한다.

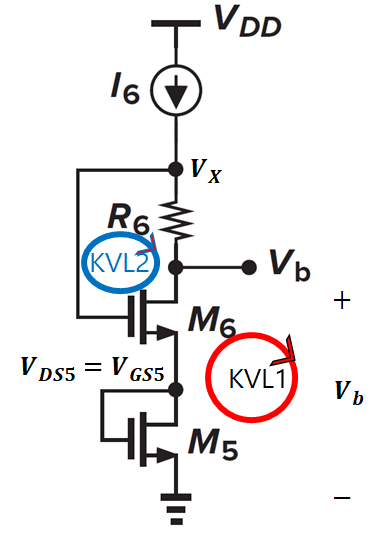

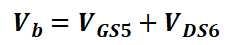

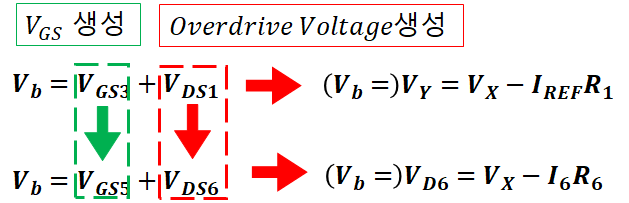

KVL1을 통해 Vb에 대한 값을 알 수 있다.

식 22에서 Vds5는 vgs5와 동일하기 때문에 바꾸어 줄 수 있다.

식 22는 식 21과 비슷함을 알 수 있고, 동일한 값이 되어야 한다.

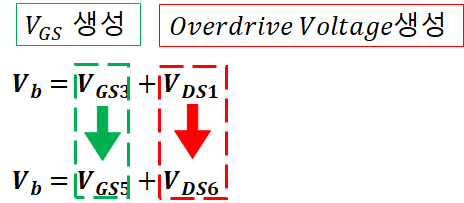

KVL 2를 통해 Vds6는 아래와 같다.(이해 편의상 Vds6로 부른 것, Vd6 전압을 구하는 것이 옳다)

따라서 사진 10은 아래와 같이 표현이 가능하다.

Vgs6과 Vgs1은 서로간에 트랙킹(Tracking)하고 각 저항의 전압강하(R1, R6)도 서로 트랙킹 함을 알 수 있다. 전류 조절도 MOS의 W/L인 사이즈의 비로 정할 수 있다.

Vb생성회로와 캐스코드 전류거울을 붙인 회로는 다음과 같다.

두번째 PVT Variation을 보완하는 Vb 생성 회로

PVT Variation에 대해 가장 큰 문제는 저항이다. Vth의 변이는 같은 mosfet을 사용하게 되면 약간의 오차는 있지만 해결할 수 있는 문제가 된다.

따라서 저항을 대신에 MOSFET를 사용해 해결할 수 있다.

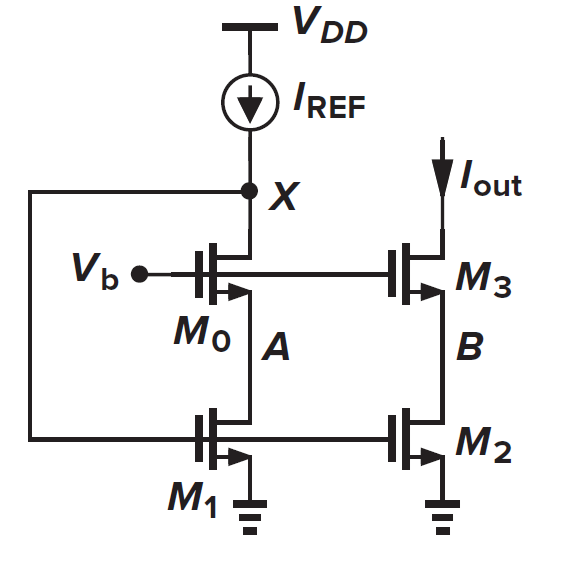

사진 13에서 기준 회로에 있었던 저항을 트랜지스터(M0)로 교체하고, 이는 포화영역에서 동작하게 해야한다.

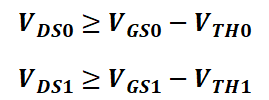

두개의 트랜지스터 M0, M1을 포화영역에 동작시키기 위한 두 가지 조건이 있어야 한다.

식 24는 다음과 같이 수정 가능하다.

식 25에서 Vb-Vgs0=Va와 같다.

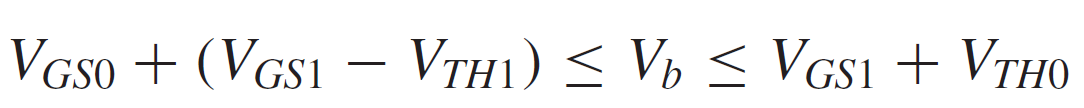

Vb에 대한 각 범위를 표현하게 되면 아래와 같이 표현 가능하다.

만약 식27과 같은 관계가 되면

M0의 오버드라이브 전압은 Vth1보다 낮아야된다.

이 과정을 통해 Vb의 입력은 M0의 오버드라이브 전압보다 같거나 커야하며, M1의 문턱전압보다 낮아야 M0와 M1을 둘 다 포화영역의 경계 또는 포화 영역에서 동작시킬 수 있다.

Vb를 생성하려면 식 27과 동일하게 Vgs0의 전압과 M1의 과구동 전압의 합의 양보다 크거나 같아야 되는 전압을 만들어주어야 한다.

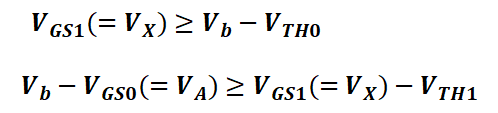

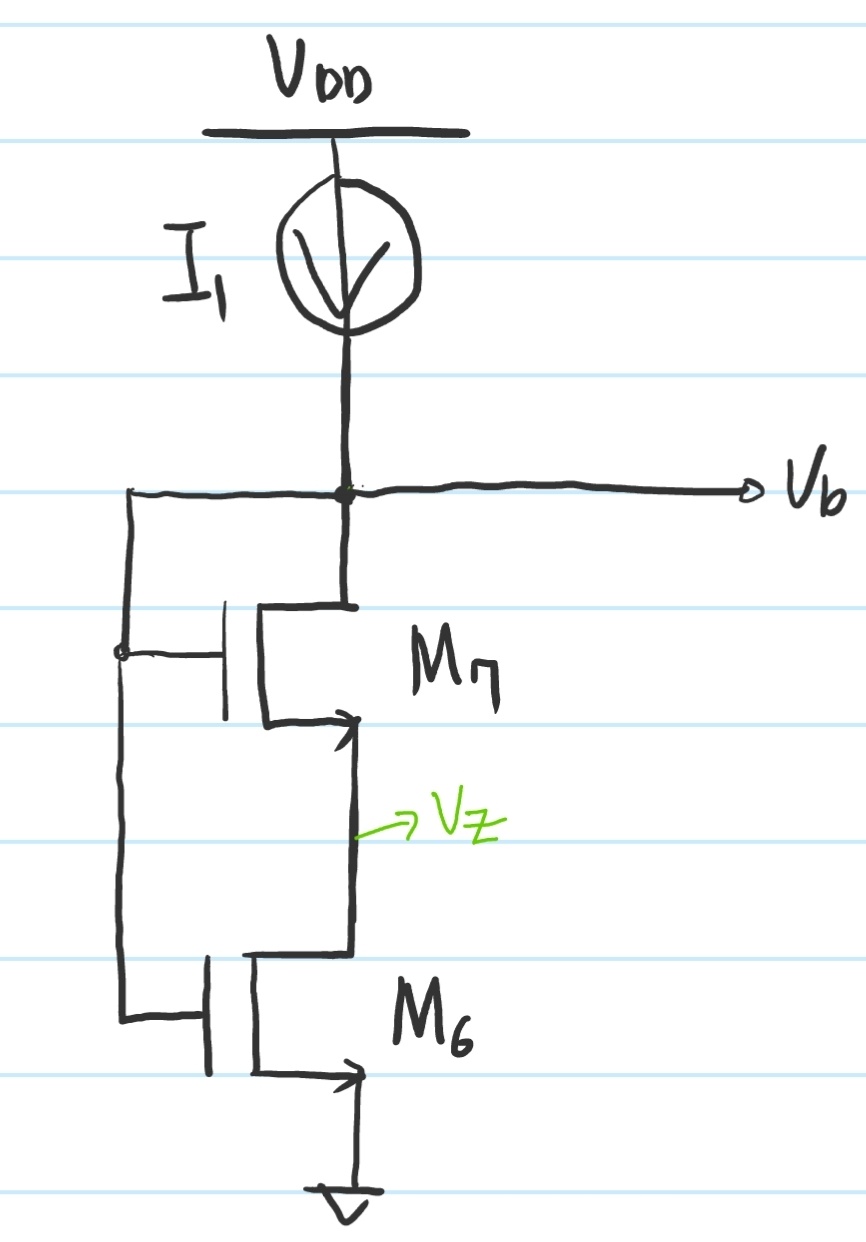

Vb 생성 회로인 사진 14를 보도록 하자

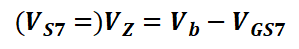

Vz에 대한 전압은 아래와 같다.

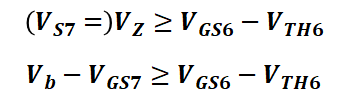

M6를 포화 영역에 동작 하게 하려면 아래의 계산 과정들을 거치게 된다.

계산 결과에 따라 따라서 Vb의 전압은 아래와 같다.

식 26, 27과 비교하여 Vgs7=Vgs0, Vgs6-Vth6=Vgs1-Vth1와 동일한 값이 됨은 알 수 있다.

이제 기준 전류회로의 Vb 생성과 R로 인해 생기는 PVT Variation에 대한 문제를 해결하였다.

이제 복사 전류회로가 어떻게 되는지 보도록 하자.

복사 전류회로도 동일하게 Vb에 대하여 풀면 식 26, 27과 동일한 값을 얻게 되고 Vgs0=Vgs3일 때 강제로 Vds1이 Vds2와 같아지게 된다.

Vb 생성회로까지 더해주게 되면 아래 사진 16과 동일해진다.

사진 16은 저전압 캐스코드로 불리며 일반적인 캐스코드보다 많이 사용된다.

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 캐스코드 증폭기, 차동 증폭기 회로 주파수 응답 해석 (0) | 2021.11.26 |

|---|---|

| 공통 소스, 소스 폴로워, 공통 게이트의 주파수 응답(Frequency response of Common Source, Gate and Source Follower) (3) | 2021.11.23 |

| 전류 거울(Current Mirror)의 원리를 알아보자 (4) | 2021.10.28 |

| 차동 증폭기 설계(Differential amplifier design) (0) | 2021.10.27 |

| 축퇴 저항 및 캐스코드 차동 증폭기 (0) | 2021.10.27 |

댓글