이 글을 위해 알아야 하는 지식

1. op amp 차동증폭기 - 차동 증폭기의 입력 임피던스

2. op amp 전압 폴로워, 반전과 비반전 증폭기

1. op amp 차동 증폭기

연산 증폭기 차동 증폭기(op-amp differential amplifier)

차동 증폭기가 왜 쓰이는지, 차동증폭기에 대한 어원은 이전에 포스팅한 글에서 확인 할 수 있습니다. (아래 링크에서는 단일 증폭기와 차동 증폭기가 어떤 측면에서 우수한지 설명하고 있다.) 2

doctorinformationgs.tistory.com

2. 반전과 비반전 증폭기와 전압 폴로워

2021.06.26 - [회로 해석 기초 지식/연산 증폭기(Operational Amplifier)] - 연산 증폭기 응용 1편(반전 증폭기와 비반전 증폭기)

연산 증폭기 응용 1편(반전 증폭기와 비반전 증폭기)

반전 증폭기와 비반전 증폭기에 대해 간단한 언급은 아래의 회로이론 실험에 간략하게 적어놓았습니다. 2021.05.11 - [실험 관련/회로이론 실험] - OP Amp 반전, 비반전 증폭기 실험 해설(회로이론 1

doctorinformationgs.tistory.com

가산기(adder)와 전압 폴로워(Voltage Follower) / OP-Amp 응용 회로

가산기(Adder) 가산기는 복수개(n개)의 입력을 받아들여 n개 입력으로부터 중첩이 된 신호를 출력으로 나오게 하는 op-amp 응용 회로중 하나이다. 이에 대한 증명은 중첩의 원리(superposition) 또는 KCL

doctorinformationgs.tistory.com

차동증폭기의 문제점

기존의 op amp 차동 증폭기를 단독으로 사용될 경우 전압 이득을 키우기 위해 입력 임피던스가 낮고 피드백 저항을 키워야 높은 이득을 얻을 수 있지만 입력 임피던스가 매우 낮음을 알 수 있는데 이는 높은 입력 임피던스를 요구하는 이상적인 op-amp와 어긋남을 알 수 있다.

따라서 이를 해결하기 위해서는 입력 임피던스를 높여주는 어떤 보조 회로가 필요함을 알 수 있다.

기존의 생각은 무한대의 입력 임피던스를 가지는 전압 폴로워(Voltage Follower)를 사용할 수 있지만 전압 이득이 1보다 작은 문제점이 발생하게 되며 좋은 대응안으로 비반전 증폭기를 사용하게 되면 무한대의 입력 임피던스를 가지는 동시에 앞에서 이득을 키워줄 수 있고 모든 이득을 단독으로 키워야만 하는 차동 증폭기의 설계 부담을 줄여 줄 수 있다.

계측 증폭기

구조

구조는 사진 1과 같이 이루어져 있다. 입력 단자부분은 위 링크에 언급된 차동 증폭기에 설명을 했으므로 간략하게 공통 입력과 차동입력 두 개의 입력원으로 이루어져있다.

A1, A2는 비반전 증폭기로 입력을 받는 비반전 단자의 입력 임피던스는 무한대로 기존에 있는 차동 증폭기의 입력 임피던스의 문제를 해결했다. A3는 차동 증폭기이다.

계측 증폭기 앞단인 비반전 증폭기의 각각의 출력 전압

A1과 A2의 비반전 단자는 OP-AMP의 특성으로 인해 각각에 입력된 전압이 똑같이 나옴을 알 수 있고 각 노드에 KCL을 적용하여 계산하면 아래와 같다.

KCL 1

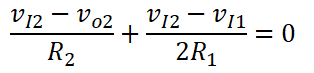

A1 증폭기 반전 단자에 있는 노드에 KCL1을 적용하면 아래와 같다.

Vout1에 대해 식을 정리하고, 식 2의 우변항과 같이 수정할 수 있다.

KCL2

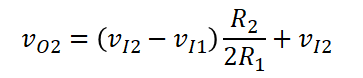

KCL2도 KCL1과 비슷한 과정이다 A2 증폭기 반전 단자에 있는 노드에 KCL2를 적용하면 아래와 같다.

Vout2에 대해 식을 정리하면 아래와 같다.

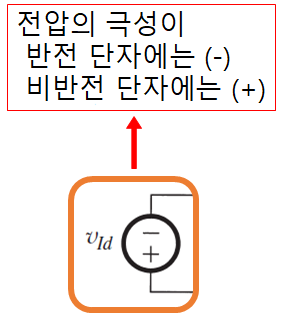

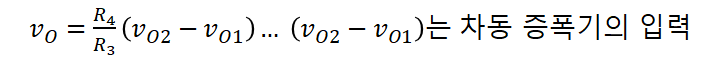

차동 증폭기 포스팅에서 차동 입력의 극성을 잠깐 상기시키면 Vout2가 차동 증폭기의 비반전 단자로 가니 (+) Vout1이 반전 단자로 가니(-)의 형태를 띄는데 이는 Vout2-Vout1으로 볼 수 있다.

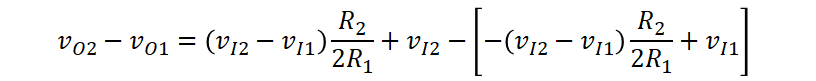

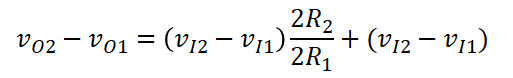

따라서 비반전 증폭기에서 나온 두 출력 전압의 차이는 아래와 같다.

식을 정리하면 아래와 같다.

두 출력 전압의 차는 아래와 같이 표현 가능하다.

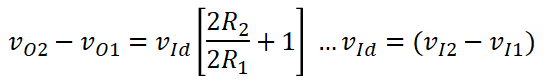

식 7로 알 수 있는 것은 사진 4와 같이 차동 전압으로 표현 가능하다.

차동 증폭기의 출력 전압

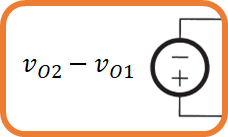

기존의 차동 증폭기의 출력 전압은 아래 식 8와 같다.

(R1, R2는 기존에 포스팅한 차동 증폭기의 저항의 비임 계측 증폭기 저항과 혼동하지 말 것)

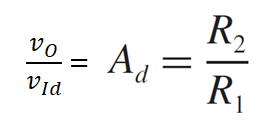

계측 증폭기 뒷단인 차동 증폭기의 출력 전압은 따라서 아래와 같이 표현 가능하다.

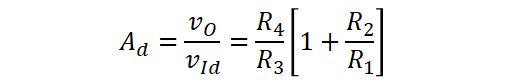

식 9에 식 7을 대입하여 계산하면

식 10은 식 8과 같이 차동이득으로 표현하면 아래와 같다.

계측 증폭기의 설계에서는 R1을 대게 가변 저항으로 두게 된다.

감사의 글

소정의 지식을 쌓는데에 도움이 되셨다면 광고 클릭을 하여 불쌍한 대학원 노예에게 10원의 기부를 부탁드립니다.

'회로 관련 전공 > 연산 증폭기(Operational Amplifier)' 카테고리의 다른 글

| 연산 증폭기(op-amp)의 입력 바이어스 전류와 오프셋 전류(input bias current and offset current)를 datasheet로 알아보자 (6) | 2022.01.06 |

|---|---|

| 연산 증폭기의 직류 오프셋(DC Offset)과 해당 datasheet를 보는법 (0) | 2022.01.06 |

| 연산 증폭기 차동 증폭기(op-amp differential amplifier) (2) | 2021.11.08 |

| 적분기와 미분기 / op-amp 응용회로 (0) | 2021.11.07 |

| 가산기(adder)와 전압 폴로워(Voltage Follower) 또는 단위 이득 버퍼(Unity-Gain Buffer) / OP-Amp 응용 회로 (0) | 2021.11.07 |

댓글