이 글은 다이오드 회로에서의 네번째 진도입니다.

이번 진도는 대신호 해석이 주(main)가 됨으로 이해하는데에 어려움이 있다면 아래 링크를 통해 참고 바랍니다.

2021.10.02 - [회로 관련 전공/회로 과정 통합 글] - 다이오드 회로의 일정전압모델 해석

다이오드 회로의 일정전압모델 해석

PN접합에서 다이오드는 전류를 흘리기 위해 문턱전압과(threshold voltage) 이상의 전압을 다이오드에 인가를 해야 전류가 흐를 수 있음을 알 수 있습니다. 일정 전압모델은 Vout/Vin 그래프를 이상적인

doctorinformationgs.tistory.com

2022.02.11 - [회로 관련 전공/회로 과정 통합 글] - 바이어스(Bias)의 의미와 PN 접합의 평형 상태, 순방향 바이어스, 역방향 바이어스에 대해 알아보자

바이어스(Bias)의 의미와 PN 접합의 평형 상태, 순방향 바이어스, 역방향 바이어스에 대해 알아보

PN 접합은 전자회로에서 아주 중요한 부분이다. 해당 글을 읽는 사람들에게 어떻게 쉽게 이해시킬 수 있을까에 대해 고민을 많이 해보았습니다. 자세한 수식 유도를 알고 싶으신 분들은 "고체전

doctorinformationgs.tistory.com

반파 정류기(Half-Wave Rectifier)

반파 정류기는 다이오드의 특성을 이용하여 어떤 정현 신호의 절반(Half)의 파형(Wave)만 출력에 나타나게(정류 하는 것을 의미) 만드는 것임으로 반파 정류기(Half-Wave Rectifier)라 부르는 것이다.

조금 더 이해하기 위해 아래 그림을 보도록 한다.

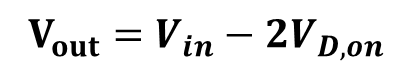

그림 1 폐회로에서 출력 전압을 알기 위해 표기된 화살표 방향으로 KVL을 적용하면 아래와 같다. 단 여기서 다이오드는 일정 전압 모델로 해석하도록 한다.

출력 전압은 입력전압과 다이오드 전압의 차임을 알 수 있다.

따라서 어떤 대신호 입력인 Vin=Asinωt가 입력이 되었을 때의 결과는 아래와 같다.

그림 2와 같은 결과를 단순 반파 정류기의 결과임을 알 수 있고, 출력 전압은 식 1과 같이 나오게 된다.

정현신호에서 양(+)의 구간에서는 다이오드의 문턱 전압 이하일 때는 스위치가 꺼져 있다가 문턱 전압보다 높은 전압의 양이 들어오게 되면 스위치는 켜지며(switch ON), 출력 전압이 나옴을 알 수 있다.

음(-)의 구간에서는 문턱전압 이하임으로 다이오드의 스위치는 꺼져(switch off) 있음을 알 수 있다.

그림 1의 단순 반파 정류기는 그림 2와 같은 문제점을 발생시키는데

이는 그림 2와 같이 상당히 변화하는 출력을 발생 시킴을 알 수 있고 전기 소자에 전력을 공급 시킬 수 없다. 따라서 일정한 출력을 만들어야 한다.

개선시키기 위한 첫번째 Step

부하 저항(Load Resistor)가 무한대의 값을 가지고 커패시터(C)를 연결한다.

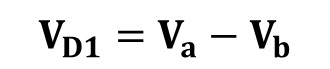

해당 제목을 가지는 회로는 아래 그림 3과 같이 표현이 된다.

그림 3에서 출력 전압은 식 1과 동일하게 입력 전압과 일정 전압으로 모델링된 다이오드 전압의 차로 형성이 될 수 있음을 알 것이다.

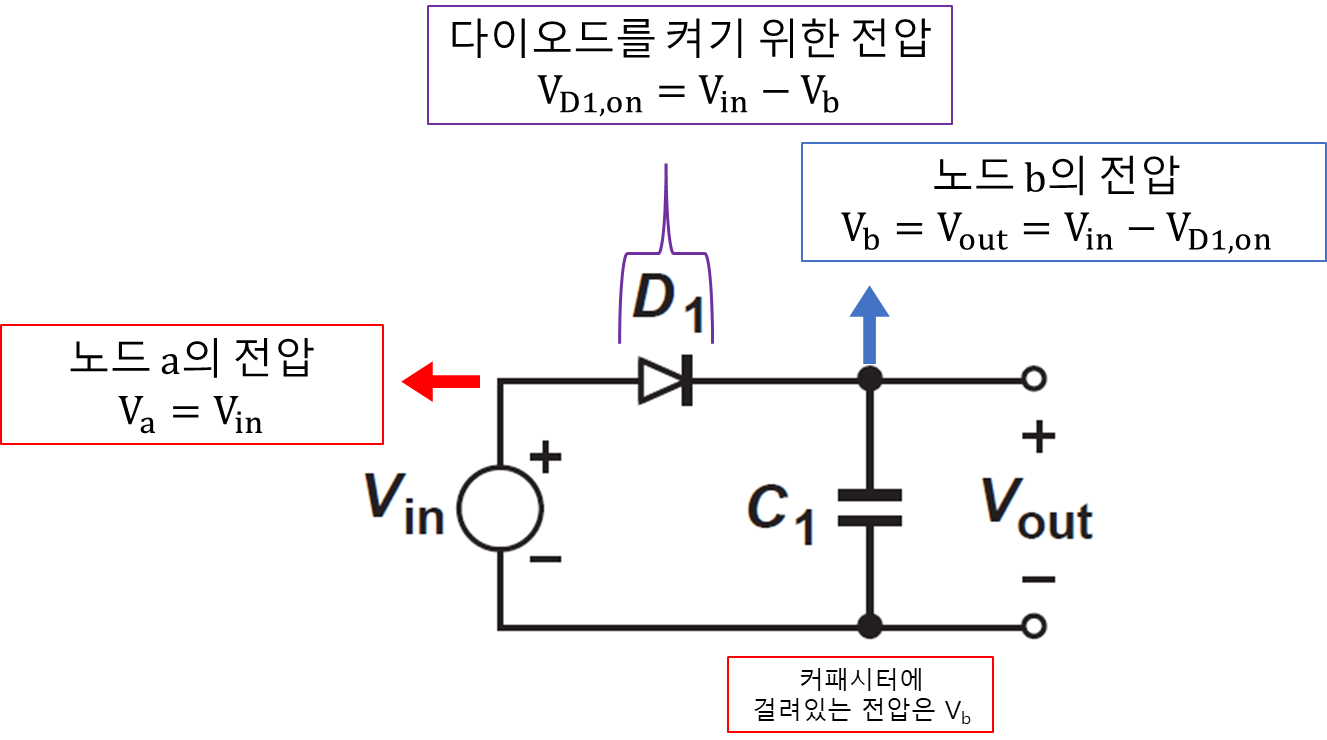

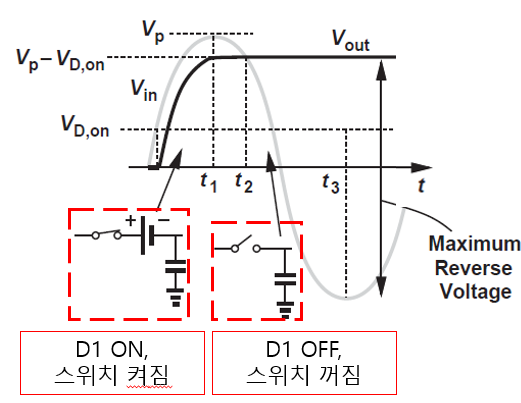

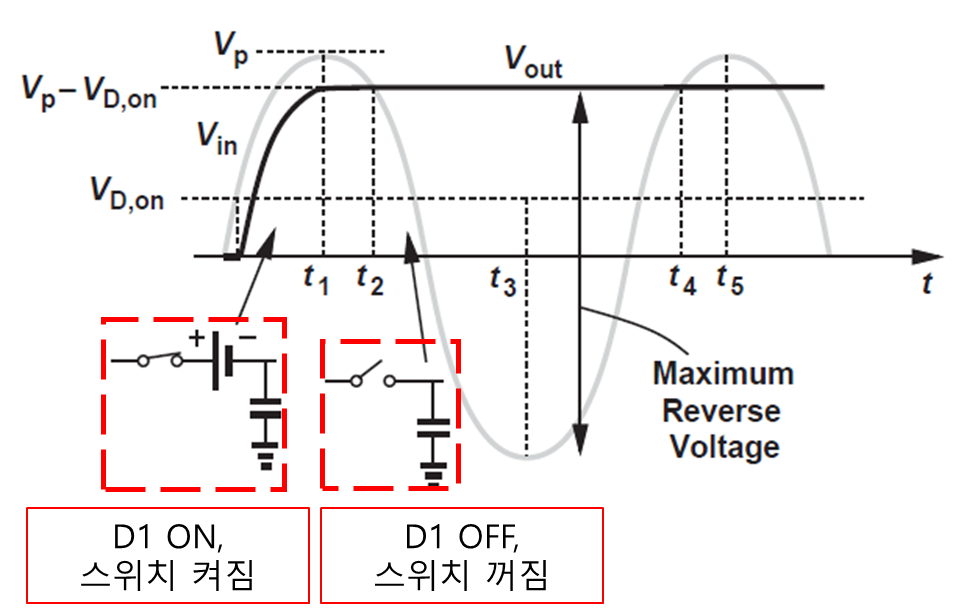

해당 결과에 각 t 구간으로 보게 되면 다음과 같은 전개가 발생한다.

t=t1 일 때 의 결과

이전 그림 1, 2와 식 1에 대해 설명 했듯이 출력 전압은 입력 전압과 다이오드의 전압의 차로 나오게 되는데 t=t1일 때 정현 신호의 최대 값(Peak값)까지는 그림 2와 동일하게 진행이 된다.

t=t2 일 때의 결과 (t1<t<=t2)

하지만 커패시터를 연결함으로써 그림 2와의 차이점은 t1<t<=t2 일 때 달라지게 지게 된다.

아래 그림 5을 보며 완벽한 회로 해석을 이해해보자

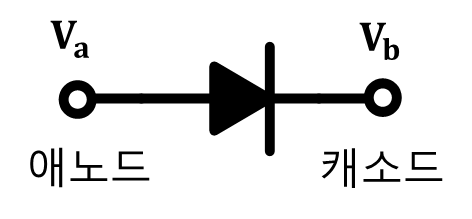

우리가 다이오드를 키기 위해서는 애노드(P)와 캐소드(N)의 두 전압 차이가 문턱 전압보다 높아야 함을 알 수 있다.

조금 더 친절하게 설명해주자면 이는 아래와 같다.

각 노드 a b에 걸린 전압이라 함은 애노드와 캐소드에 걸린 전압을 의미하게 되는 것이다.

따라서 다이오드에 걸린 전압은 아래와 같이 표현이 가능하다.

그 다음으로는 커패시터에 대한 설명인데 커패시터는 에너지 저장 소자이기 때문에 충전과 방전을 하게 되는데 방전하는 경로가 없다면 커패시터는 충전이 된 상태(충전된 전압을 가지고 있는 상태)로 유지가 된다.

두 소자(다이오드, 커패시터)에 대한 내용을 다시 상기시켜 보았고 Peak값을 도달한 t1에서 조금 더 시간이 지난 t1+a 상태일 때의 전압을 해석해보면 그림 6과 같다.

그림 6과 같이 커패시터는 충전이 되어있고 방전하려는 경로가 없다. 따라서 커패시터가 연결된 노드 b는 충전된 전압 즉 그림 6에서 표현된 Vb의 값을 그대로 가지게 된다.

Vin(노드 a 전압)의 전압은 t=t1+a임으로 충전된 커패시터의 전압 값 Vb(노드 b)보다 낮아짐으로 다이오드는 역방향 바이어스가 걸리게 됨으로 꺼진다.(Switch off) 이에 대한 설명은 그림 6 보라색 박스에 적혀있다.

이에 대한 결과는 그림 7로 표현한다.

t=t3 일 때의 결과

t=t3일 때는 입력 정현 신호가 음의 값이 최대(peak) 값에 도달 했을 때이다.

이는 그림 8로 표현이 가능한데 t=t3일 때 다이오드의 항복 전압에 관한 문제점이 발생할 수 있다.

그림 8에서 입력 전압 Vin(=Va)은 그림 6에 보이는 전압원의 극성 방향은 t=t3 일 때(정현 신호가 음의 구간으로 갈 때) 반대로 가게 바뀌게 된다.

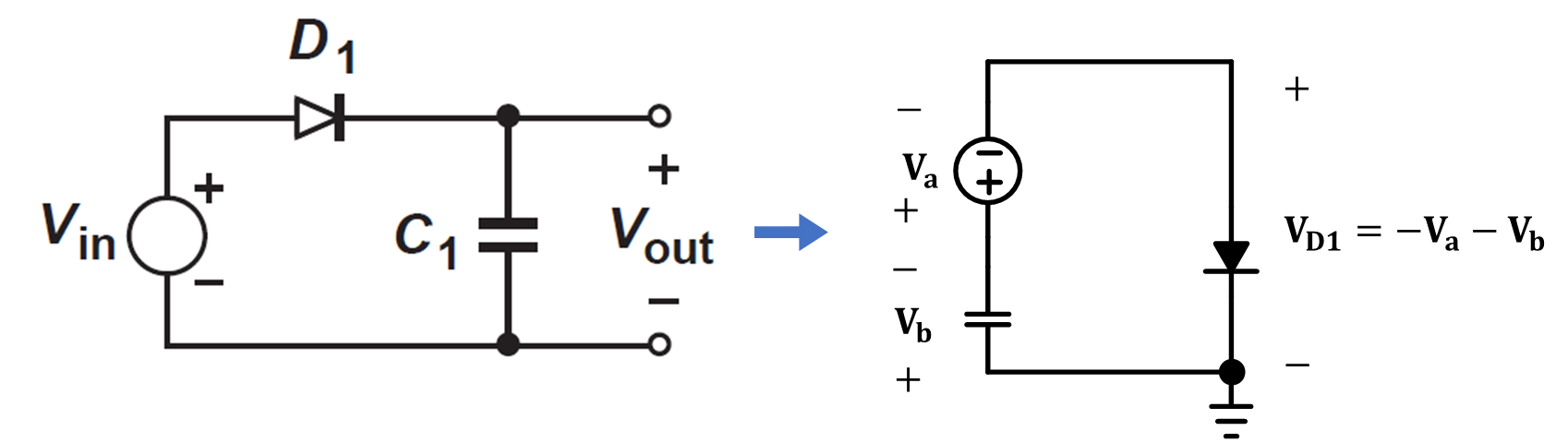

회로로 표현하게 된다면 그림 9와 같이 표현이 가능하다.

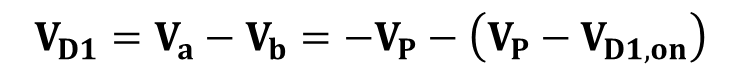

우측에 보이는 회로는 극성이 바뀐 회로이고 폐회로에 대해서 KVL을 적용하게 되면 다이오드에 걸린 전압은 아래 식 3으로 표현된다.

식 3 우 항의 첫째 항은 전압원, 두번째 항은 커패시터에 걸린 전압이다. 따라서 다이오드는 큰 역방향 전압을 버틸 수 있어야 한다. 그렇지 못하면 항복현상이 발생해 큰 전류가 흐른다.

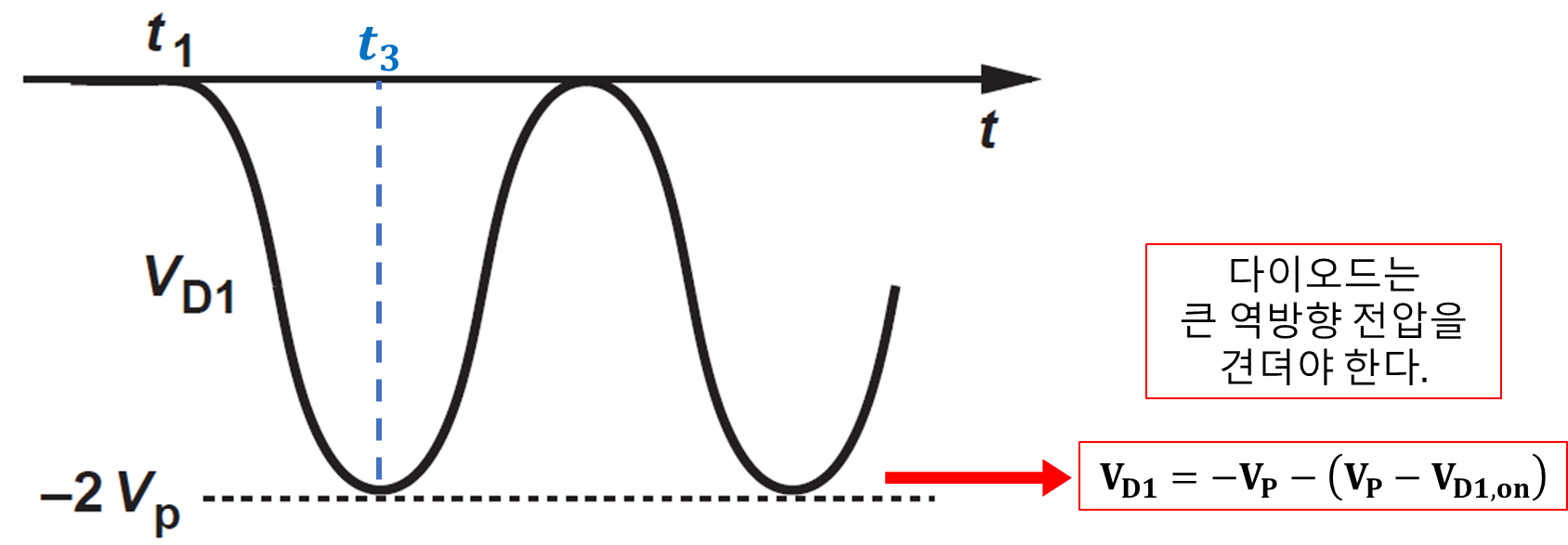

t가 t1 ~ t3 에서 생기는 다이오드에 걸리는 전압의 변화를 표현하면 그림 10과 같다.

t=t4 와 t=t5 일 때의 결과

t=t4, t=t5 일때의 결과와 여태 정리했던 내용에 대해 정리한 그림은 아래와 같다.

t=4일 때는 식 3을 참고하여 아직 다이오드는 켜질 수 없을을 의미한다.

t=t5 일 때 식 3을 참고해서 다이오드를 킬 수 있다. 하지만 t=t5+a=t2+a와 같음으로 바로 다이오드가 꺼지는 현상이 발생한다.

이 부분을 다시 정리해서 적게되면 커패시터의 방전 경로가 없다면 커패시터는 계속 충전된 상태를 만들기 때문에 출력 전압은 일정하게 유지함을 알 수 있지만 다이오드의 역전압을 버티는 문제점과 실제 회로를 구현할 때 부하 저항의 효과를 고려해야한다.

개선시키기 위한 두번째 Step

부하 저항(Load Resistor)가 유한한(finite) 값을 가지고 커패시터(C)를 연결한다.

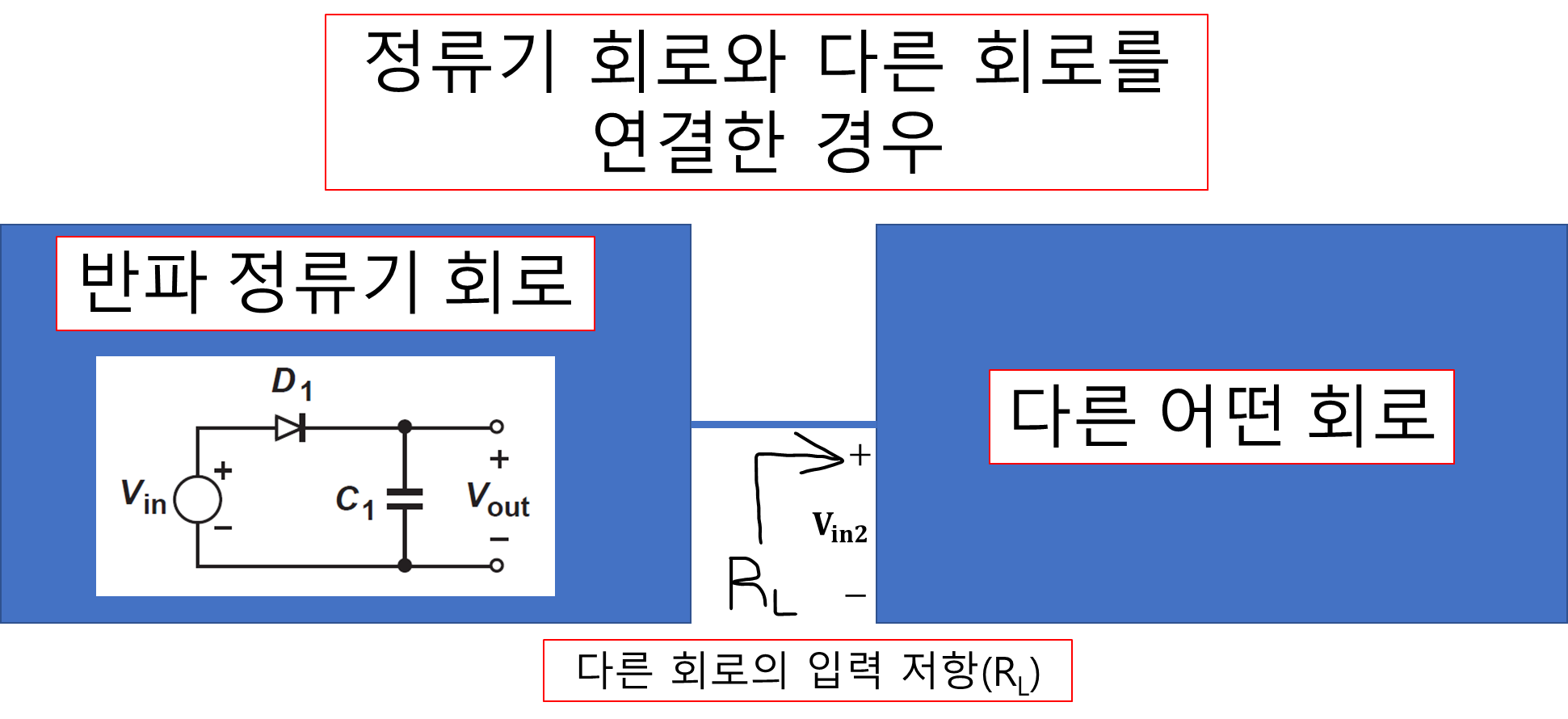

부하 저항에 대한 개념을 이해하기 위해서 그림 12을 보도록 한다.

그림 12와 같이 반파 정류기와 다른 어떤 회로(편의상 A로 부름)랑 연결 했다고 가정하자.

이 A 회로는 입력 저항(Rin or Zin)을 가지고 있는데 A 회로에 입력 저항에 걸리는 전압(Vin2)은 반파 정류기 회로의 Vout이 된다(병렬 전압은 같기 때문에). 이는 아래와 같이 적을 수 있다.

회로를 설계 할 때 전 단(Previous Stage)인 반파 정류기 회로의 출력 전압이 다음 단(Next Stage)에 걸리는 전압을 결정하고, 원하는 값에 맞게 구동시켜야 하기 때문에 부하저항(RL)은 중요하다.

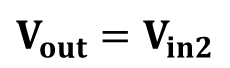

조금 더 쉽게 표현하기 위해서 그림 12는 아래 그림 13과 같이 수정한다.

유한한 저항을 가짐으로써 어떤 결과를 가져올까?

답은 기존의 커패시터가 방전을 하는 경로가 존재하지 않았지만 유한한 부하 저항이 생김으로써 방전함을 알 수 있다.

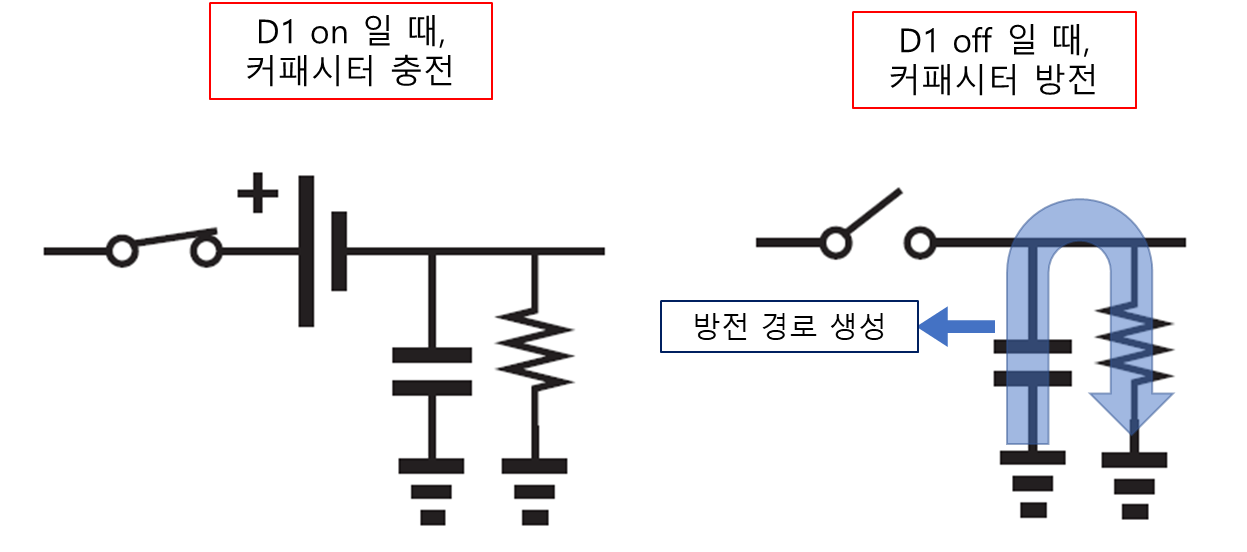

이는 아래와 같다.

위에서 다루었던 t1 부터 t5 까지의 내용들을 다시 한번 해 보도록 하자. 위에서 언급한 각 t1을 제외한 나머지인 t2 ~ t5와 똑같은 지점이 아니니 혼선이 없길 바란다.

t=t1 일 때

식 1과 동일한 결과와 그래프를 가지게 된다.

t=t2 일 때

정현 신호의 한 주기가 끝나고 다시 양의 구간으로 올라 갈 때 Vin=Vout이 같아지는 지점을 t2라 한다.

이전 부하 저항이 없을 때는 커패시터가 방전 경로가 없기 때문에 고정이 되었지만 부하 저항을 추가함으로써 방전 경로가 생기고 충전된 전압은 지수함수적으로 전압이 떨어짐을 알 수 있다.

이에 대한 결과는 아래와 같다.

입력 전압과 출력 전압이 같아지는 지점에서는 다이오드 애노드와 캐소드의 전압차가 0이기 때문에 다이오드의 전원을 킬 수 없다.

이해가 어렵다면 식 3으로 되돌아가길 바란다.

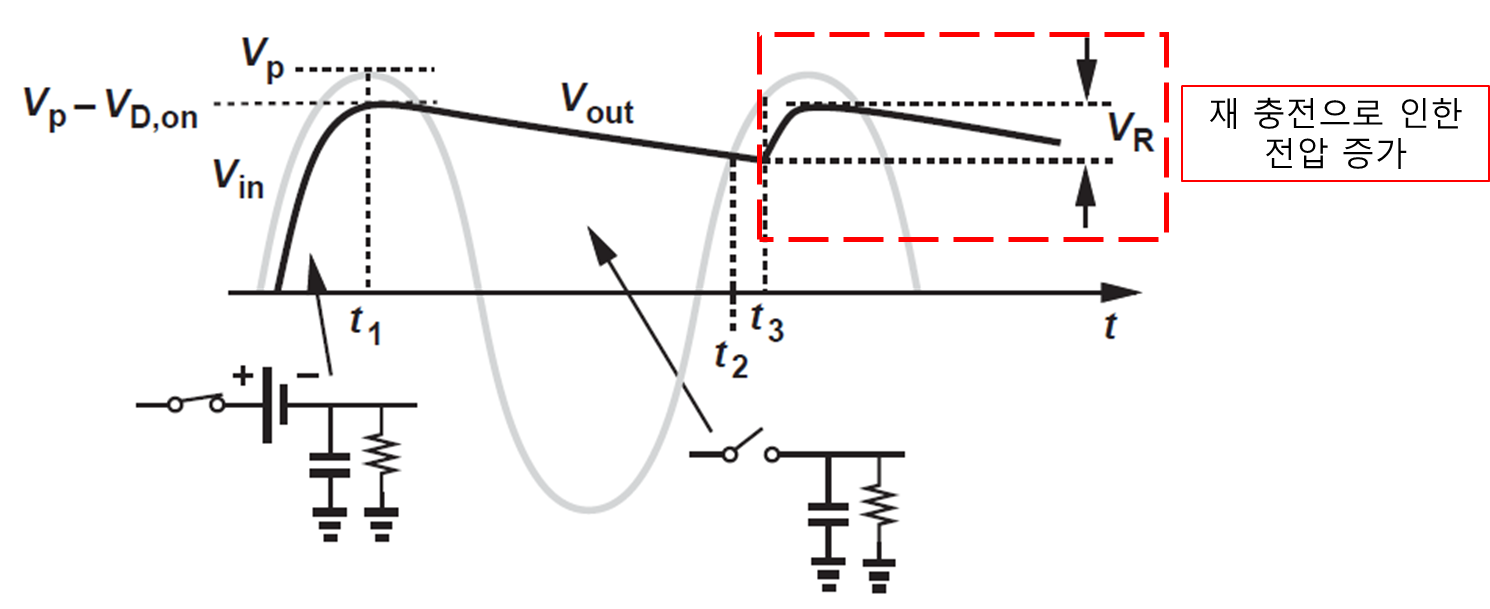

t=t3 일 때

t3의 의미는 t2보다 큰 입력전압을 가지며 t3 지점은 식 3에서 VD1이 VD1,on과 같아지는 지점을 의미한다.

부하 저항에 걸리는 전압(VR)은 커패시터의 전압 충전으로 인해 다시 증가하고 입력 전압(Vin)이 최대 값을 찍고 내려갈 때 똑같이 내려간다.

출력 전압(Vout)의 변화는 리플(ripple)이라 부르며 리플의 피크 대 피크(Peak to Peak)는 5~10% 아래에 유지되어야 한다.

리플(ripple)에 대해 조금 더 알아보도록 하자.

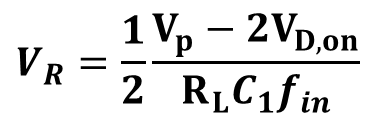

리플(Ripple)의 크기(Amplitude)

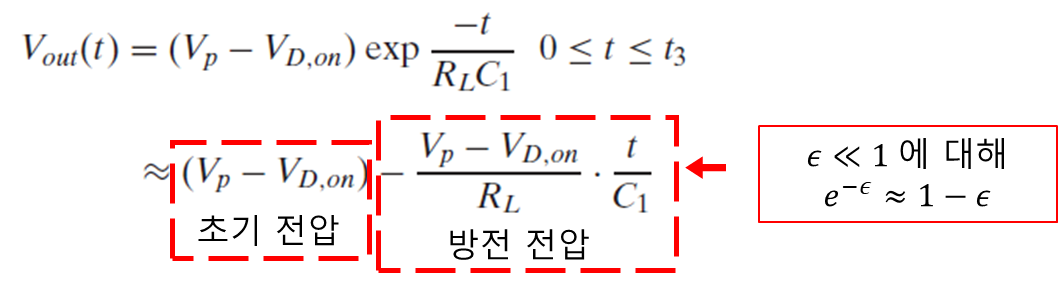

수식의 증명은 다소 생략하고 결과 중심으로 적겠습니다.

그림 16에서 t3까지의 방전을 수식적으로 표현하면 아래와 같다.

출력 전압에는 두가지 성분이 있는데 우항에 첫째항은 초기 전압, 두번째 항은 커패시터로 인해 방전되는 전압을 의미하게 된다.

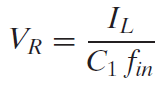

두번째 항을 VR로 표현하고 풀어서 정리하면 아래와 같이 간략하게 표현이 가능하다.

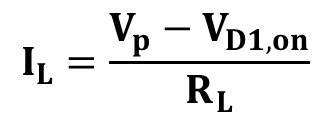

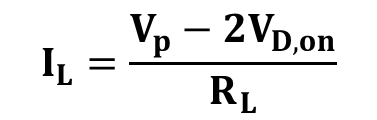

식 6에서 fin은 입력 주파수, IL은 부하에 흐르는 전류를 의미하게 된다. 부하 전류는 아래와 같다.

식6과 7을 고려해보면 리플의 크기를 줄이려면 주파수를 올리는 방법을 가지고 있고, 부하 저항과 커패시터의 크기를 키우는 세 가지 방법이 있음을 알 수 있다.

다음 진도로는 전파 정류기에 대해 알아볼 것이다.

전파 정류기(Full-Wave Rectifier)

전파 정류기는 무슨 의미이지?

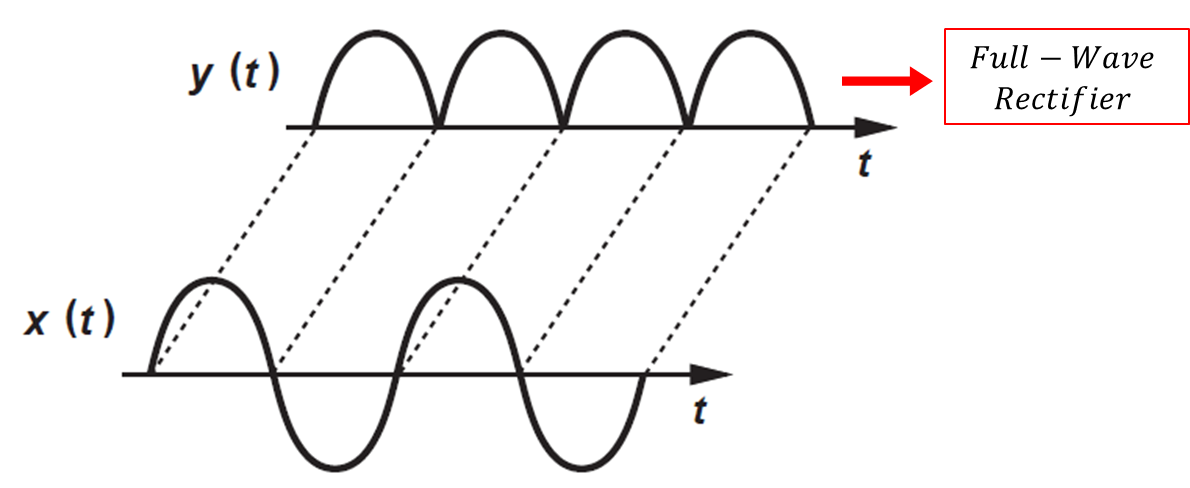

전파 정류기의 의미를 알기 위해서 반파 정류기를 다시 생각해보자 반파 정류기는 어떤 정현신호의 양의 구간에서만 다이오드가 동작함을 알 수 있었다. 하지만 리플의 크기를 줄이려면 R, C, 주파수가 높아야 작아질 수 있는데 흔히 우리가 쓰는 어댑터들은 고정된 주파수를 사용하기 때문에 RC를 키운다. RC를 키우게 되면 칩의 면적이 증가하는 문제점이 생기며 어떤 정현 신호의 '음의 구간'을 양의 구간으로 출력시킨다면 리플의 크기를 절반으로 줄일 수 있다.

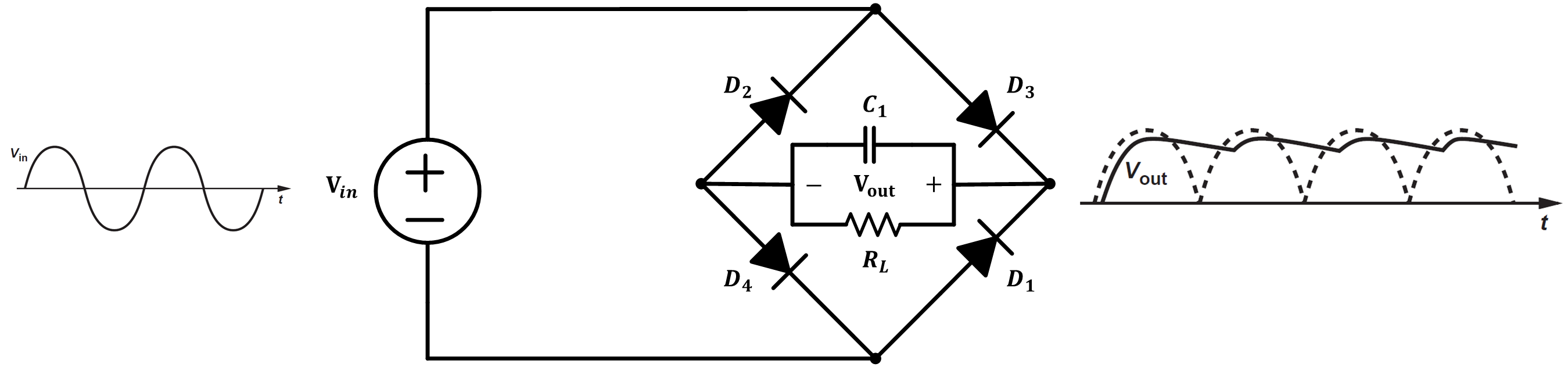

따라서 정현신호의 양과 음의 구간을 모두 양의 구간인 출력으로 내보내기 위해 만들어진 정류기를 전파 정류기(Full-Wave Rectifier)라고 하며 브리지 정류기(또는 브릿지 정류기, Bridge Rectifier)라고도 불린다.

간단한 개념 설명에 대해서는 그림 17을 통해 알 수 있다.

아직 커패시터를 고려하지 않는 전파 정류기

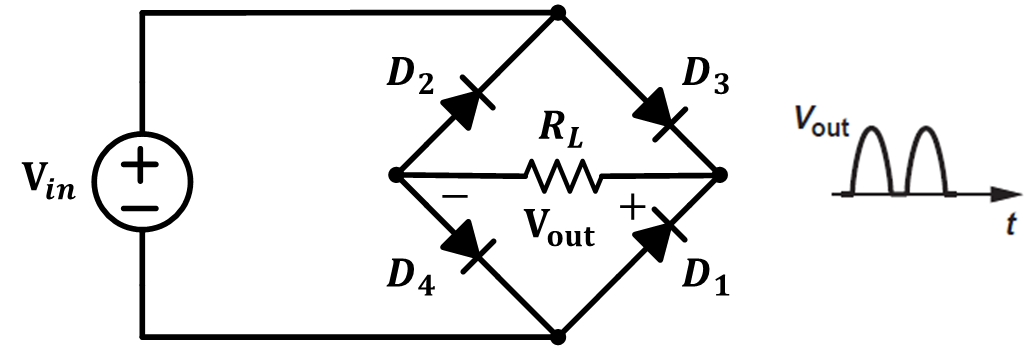

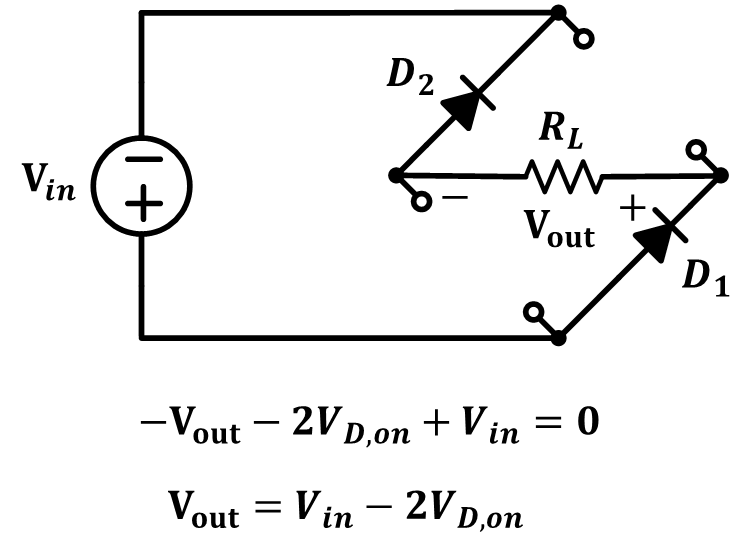

아래 그림 18은 커패시터를 고려하지 않는 전파 전류기이다.

그림 18은 기존 반파 정류기에 비해 다이오드가 3개 더 추가된 것을 볼 수 있으며 Vout은 2VD,on만큼 차감 되어 출력이 될 것을 암시하고 있다.

계산을 통해 확인해 보자

1) 정현 신호가 양의 구간일 때

그림 19는 정현신호가 양의 구간의 피크 전압일 때의 등가 회로이다. KVL(파란색 선)을 적용하면 아래와 같은 결과가 나오게 된다.

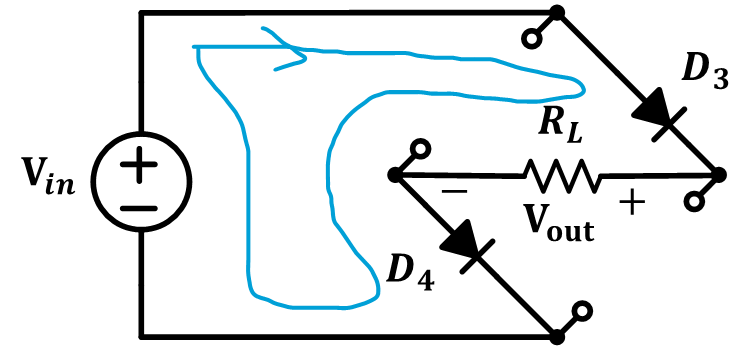

2) 정현 신호가 음의 구간일 때

음의 구간일 때 또한 KVL을 적용해보면 식 9는 식 8과 같음을 알 수 있다.

정리해보면

음의 구간에서는 -1이 곱해져서 음의 입력이여도 출력에서는 양의 출력이 나옴을 알 수 있고, 정현 신호의 양과 음의 구간을 둘 다 양의 구간에서 출력 시킬 수 있어 리플의 크기를 보다 작은(물리적 크기) RC의 값으로 줄일 수 있다.

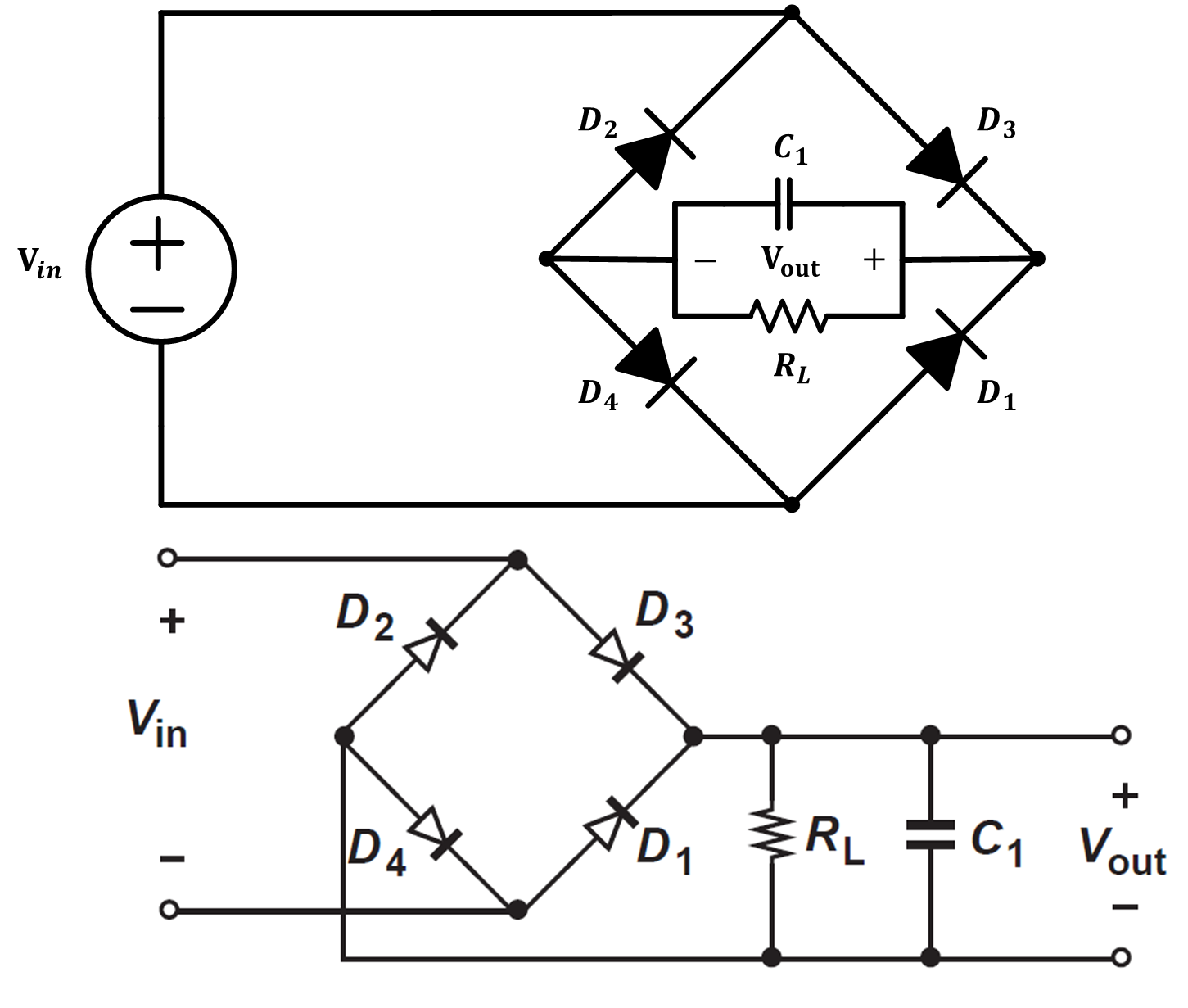

커패시터를 포함한 전파 정류기

커패시터를 포함한 전파 정류기는 아래 그림 21과 같다.

그림 21이 보기 불편한 경우 아래 그림 22와 같이 보기 쉽게 수정이 가능하다.

전파 정류기에서 출력에 흐르는 부하 전류는 두 다이오드에 의한 영향을 받음으로 식 7은 식 10과 같이 변경이 된다.

그리고 식 10이 변경이 되고 주기가 반으로 줄었음으로 식 6도 아래와 같이 변경이 된다.

그림 16과 같이 입력과 출력에 대한 특성 및 회로와 함께 표현을 하자면 아래 그림 22와 같음으로 전파 정류기의 입출력 특성을 확인 할 수있다.

전자회로 1 과정을 학습하셨습니다.

아래 링크를 통해 다음 진도와 전자회로 1의 모든 내용을 확인하실 수 있습니다.

2022.01.13 - [전공(Major)/전자회로 1 과정] - 전자회로 1 커리큘럼

전자회로 1 커리큘럼

전자회로 1 커리큘럼입니다. 기본적으로 반도체 공학에서 배웠던 능동소자(Diode, BJT, MOSFET)를 통해 단일 증폭기를 설계한다. 회로를 해석하는데에 있어 회로이론에서 배운 회로 해석기법을 사용

doctorinformationgs.tistory.com

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| BJT의 소신호 등가모델(Small-Signal Equivalent Model) (0) | 2022.03.06 |

|---|---|

| 다이오드 클리퍼 회로와 클램퍼 회로 (한계 회로와 직류 복원기) (0) | 2022.03.05 |

| 다이오드의 대신호(Large-Signal)와 소신호(Small-Signal) 동작에 대해 알아보자 (0) | 2022.02.17 |

| 바이어스(Bias)의 의미와 PN 접합의 평형 상태, 순방향 바이어스, 역방향 바이어스에 대해 알아보자 (0) | 2022.02.11 |

| 드리프트(Drift), 확산(Diffusion), 전류밀도(Current Density)에 대해 알아보자 - 전자회로 기초 (0) | 2022.01.28 |

댓글