이 글은 차동 증폭기 설계에서 주파수 응답이 포함된 글입니다.

2021.10.27 - [전공(Major)/전자회로와 아날로그 회로설계] - 차동 증폭기 설계(Differential amplifier design)

차동 증폭기 설계(Differential amplifier design)

2021.10.25 - [전공(Major)/전자회로와 아날로그 회로설계] - Common Source Amplifier Design(공통 소스 증폭기 설계) Common Source Amplifier Design(공통 소스 증폭기 설계) 회로의 구성은 위와 같다. 공통 소..

doctorinformationgs.tistory.com

설계 절차

1. 토폴로지 선택(저항, 캐스코드, 축퇴형)

- 제일 간단한 저항성 부하를 먼저 선택하는 것이 좋다.

2. Length를 선택

- 해당 공정에서 제공하는 가장 낮은 L을 선택하는 것이 좋다.

3. Vov를 선택

4. 키 디자인 방정식으로 부터 드레인 전류를 구한다.

5. 바이어스 전류를 위한 W와 부하저항을 계산한다.

1) W

2) 부하저항

목표

Capacitive Loading CL로 구동되는 차동 전압 증폭기를 설계하고 GBW를 만족시키는것

(GBW=A*w_BW ... w_BW =2*pi*f_BW)

키 디자인 방정식

이득과 대역폭(f_BW)을 만족하고 CL을 구동시키기 위한 바이어스 전류(Iss)의 크기를 찾아야한다.

1-1) 이득

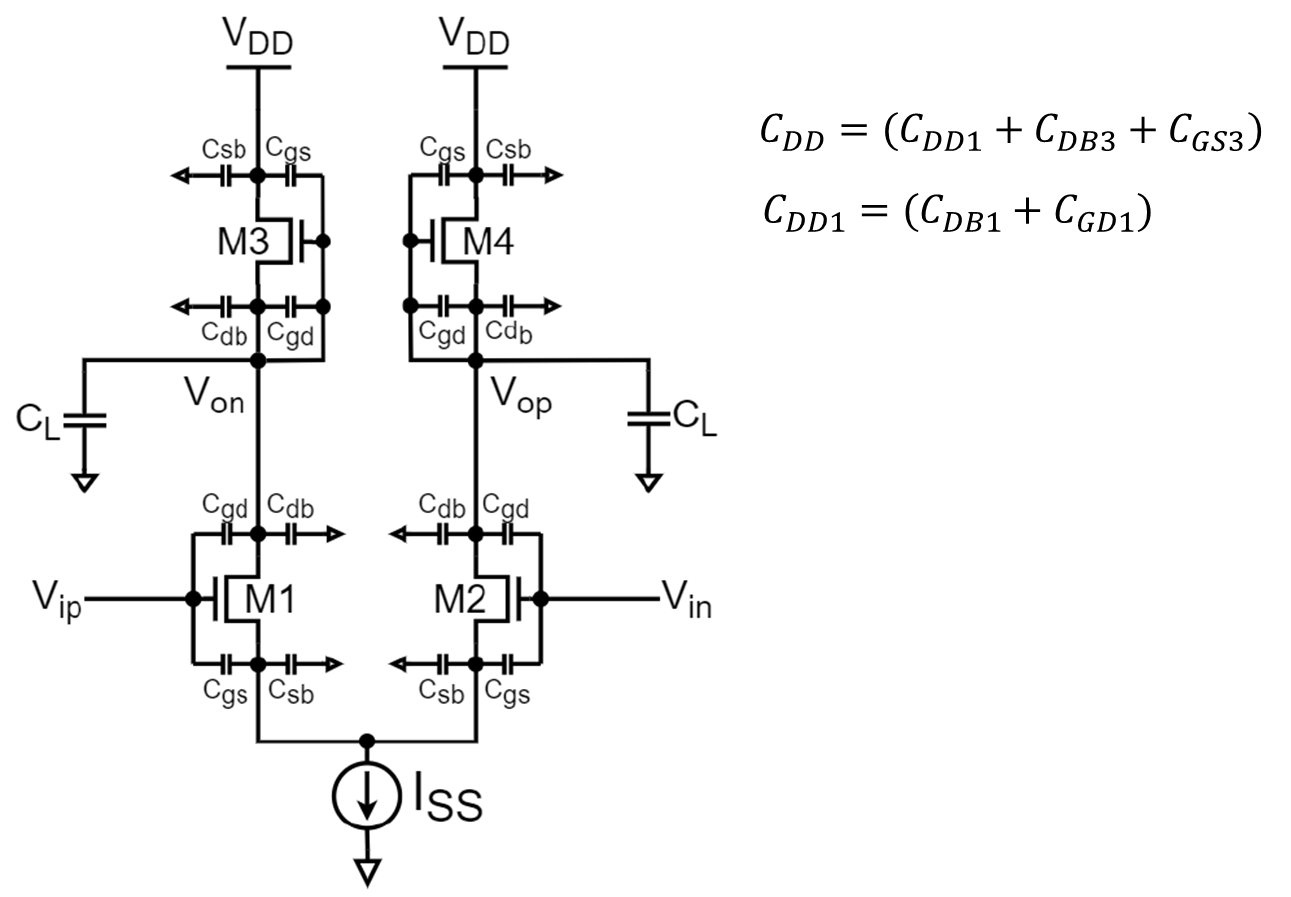

사진 2와 같이 절반회로를 적용하면 CS Amp에서 얻었던 전압 이득을 알 수 있다.

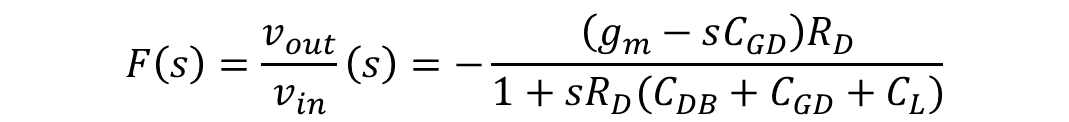

지난 포스팅에서 구했던 cs amp의 이득은 식 1과 같다.

DC gain은 gmRD임을 다시 상기하는 것도 중요하다.

공통 소스, 소스 폴로워, 공통 게이트의 주파수 응답(Frequency response of Common Source, Gate and Source Follo

이번 Chapter 6의 내용은 밀러 근사를 이용하지 않고 KCL을 통해 극점과 영점을 전부 보는 연습을 하도록 한다. 밀러 근사를 이용하는 건 Stability를 다루는 챕터에서 많이 다루도록 한다. 이번 포스

doctorinformationgs.tistory.com

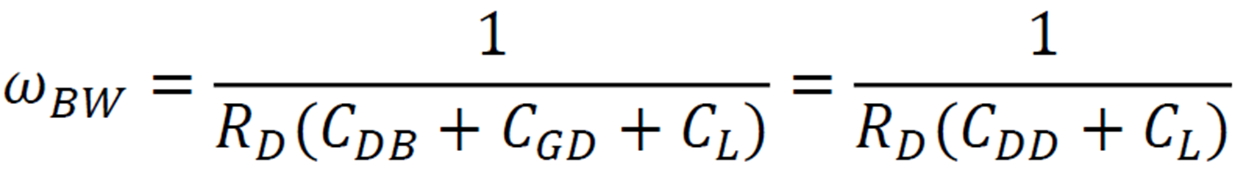

1-2) 대역폭(BandWidth)

대역폭은 식 2와 같으며 해당 과정은 지난 설계에서도 여러번 반복했음으로 자세한 과정은 생략한다.

CDD는 아래와 같다

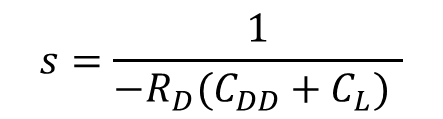

w_BW의 dominant pole(주 극점)은 식 1과 2에서 알 수 있다.

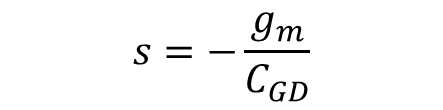

Zero(영점)는 아래와 같다.

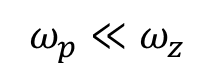

여기서 중요한 점은 영점은 식 2보다 매우 커야하는데

첫번째는 전압이득을 1보다 크게 설계하기 위해서는 드레인 저항이 1/gm보다 훨씬 크기 때문이며

두번째로 극점은 기생 커패시턴스의 합과 드레인 저항의 곱으로 표현되기 때문에 아래와 같은 관계가 성립된다.

위와 같은 이유로 현재 차동 증폭기의 대역폭에서 zero(영점)의 영향을 무시할 수 있다.

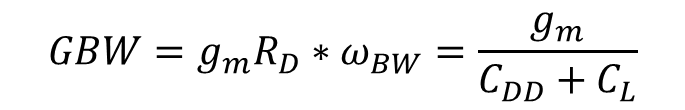

마지막으로 이득 대역폭곱(GBW)을 아래와 같이 표현 가능하다.

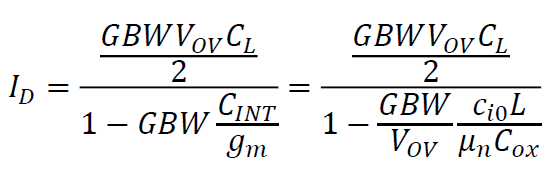

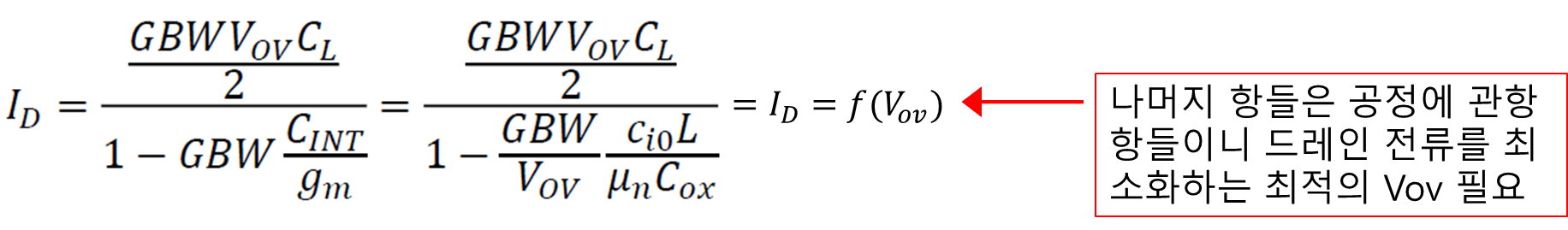

1-3) 드레인 전류 Id

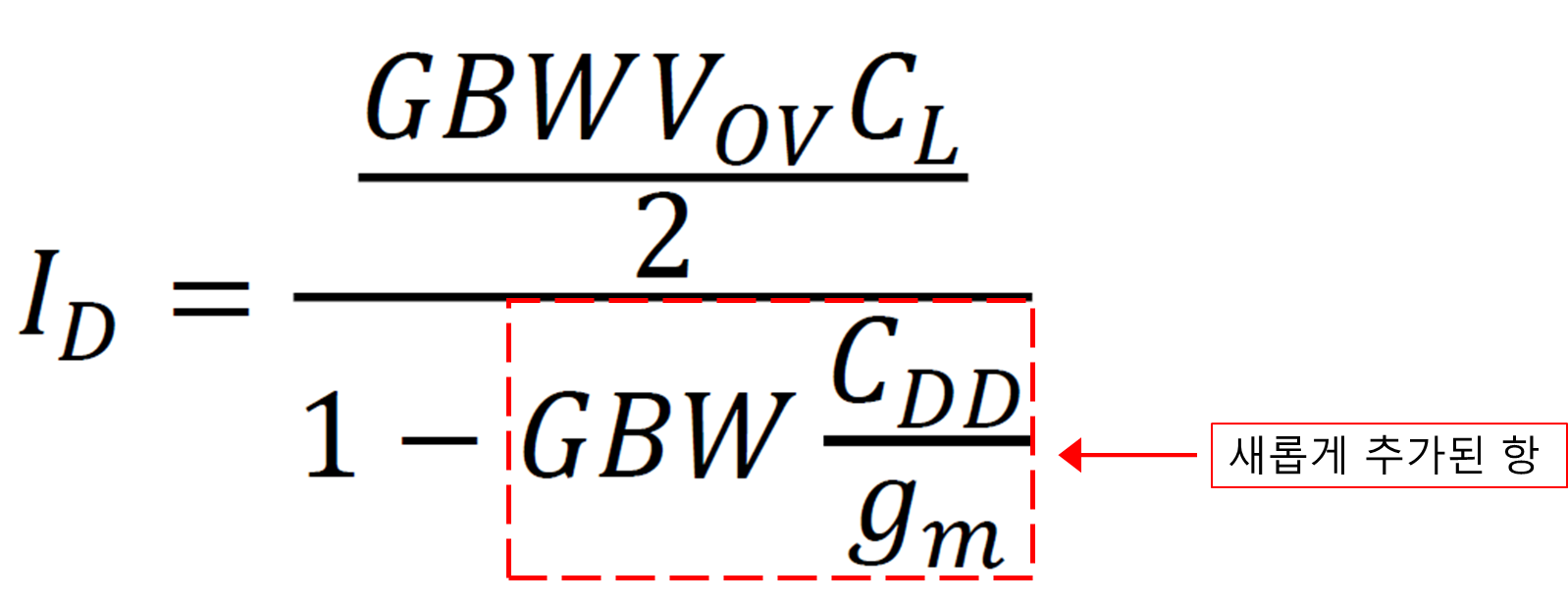

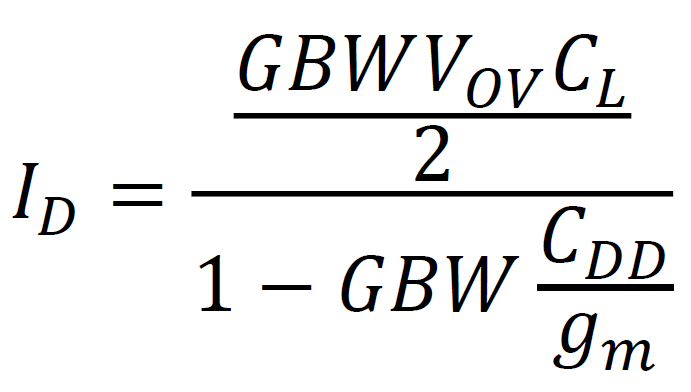

결과부터 말하자면 식 6으로 표현 가능하다 증명과정을 중간에 넣게 되면 번잡할 수 있으니 증명과정을 아래에 첨부할 것이다.

식 6을 통해 분자는 기존에 포스팅한 차동증폭기의 드레인 전류 식과 동일하지만 분모가 새로 추가됨을 알 수 있으며 분모의 항이 0에 가까워질수록 드레인 전류가 증가함을 알 수 있다.

자세한 내용은 맨 하단에 부록 1에 자세히 언급이 되어 있으니 호기심이 생긴다면 읽어보는 것이 좋다.

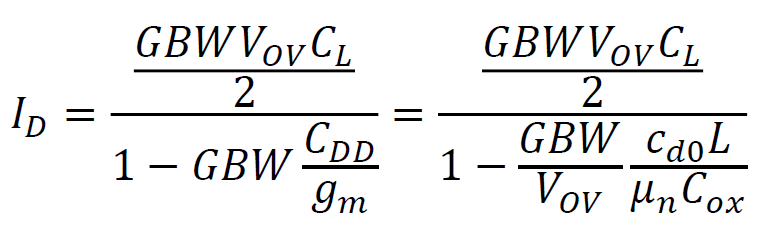

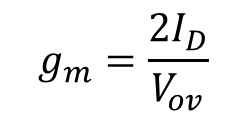

MOSFET가 Long-Channel Device인 경우 Id=0.5µCox(W/L)Vov^2 로 표현이 가능하며 gm은 드레인 전류를 미분한 형태임을 mos 물리에서 알 수 있었다. CDD=C_d0*W로 표현가능하다.

따라서 식을 아래와 같이 Long Channel Device로 표현한 수식으로도 표현가능하다.

본인이 원하고자 하는 GBW가 매우 낮은 경우에는 차동 증폭기 설계 포스팅에서 알 수 있듯이(식6의 분자)로 간략한 형태로 표현 가능하다.(Id=GBWVovCL/2)

그리고 드레인 전류를 키우기 위해 Vov를 키우면 전력소모는 증가하지만 트랜지스터는 좀 더 빨라진다.

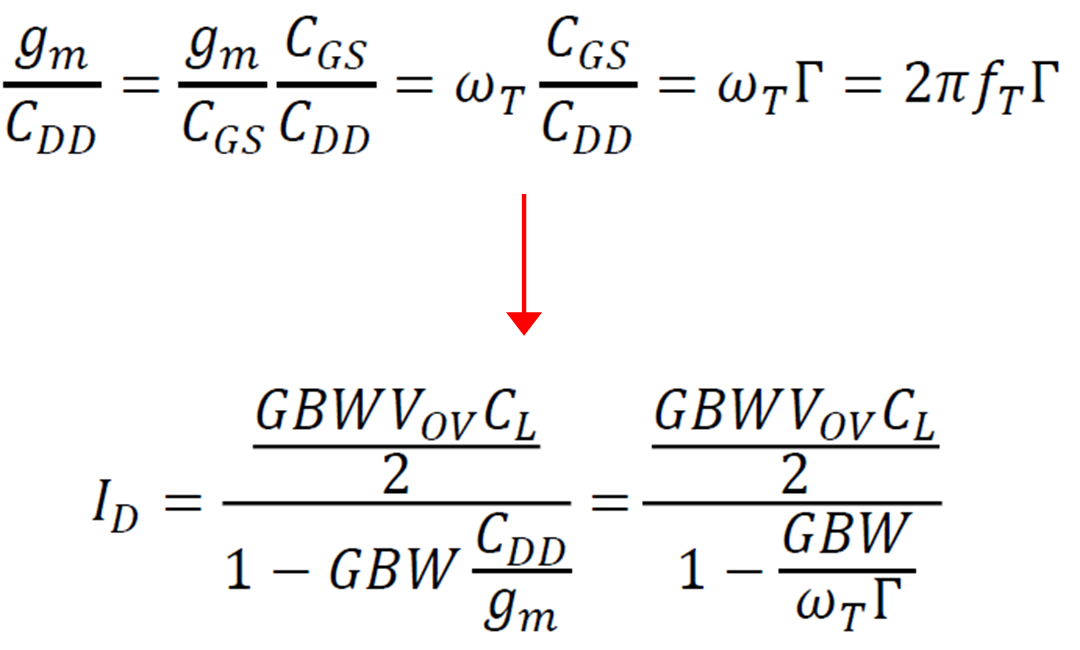

추가적인 요소로 식 6의 분모항을 천이 주파수형태의 꼴로 표현이 가능하다.

다이오드 연결 부하를 가지는 차동 증폭기

아래 회로를 간단하게 알아보자.

기존의 CDD가 어떤 값을 변경되었는지 확인해 볼 수 있다.

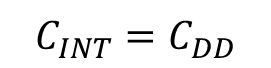

드레인 전류는 아래와 같이 나오게 된다.

식 9에서 CINT는 진성 커패시턴스(도는 Self 커패시턴스)를 의미하며 식 9를 통해 다이오드 부하를 가지는 경우 부하 저항을 사용하는 것보다 좋지 못한 성능을 가지고 있음을 알 수 있다.

저항성 부하를 사용하는 경우는 진성 커패시턴스는 아래와 같다

Long-Channel Device인 경우

식 11은 식 7과 유사함을 알 수 있으며, d의 표기는 i 즉 진성(intrinsic)을 표현한다.

키 디자인 방정식 - 최적의 Vov

식 11 우항을 보게 되면 Vov 외에는 공정에 관한 항들임을 알 수 있다.

따라서 드레인 전류를 최소화하는 최적의 Vov 전압이 필요하다.

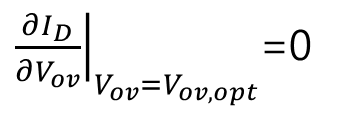

미분한 양이 0이 되어야 최적 지점이다.

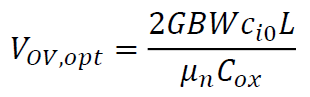

따라서 최적의 Vov는 아래와 같다.

하지만 여기서 문제점이 있는데 Vov<50mV 이하일 때, 게이트-소스 전압(Vgs)는 문턱전압에 진입할 때 약 반전 영역이기 때문인 문제점을 포함하여 여러가지 문제들을 가지기 때문에 최소 100mV 를 인가해주어야 안정적인 동작이 가능하다.

따라서 Vov 최적화의 조건은 아래와 같다

식 14의 우항은 Vov,opt는 50mV 임을 상기하자

Id 증명과정

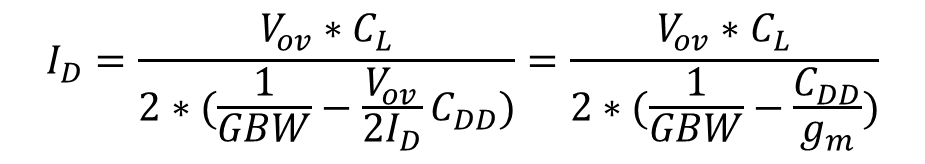

식 5에서 gm은 아래와 같이 표현 가능하다.

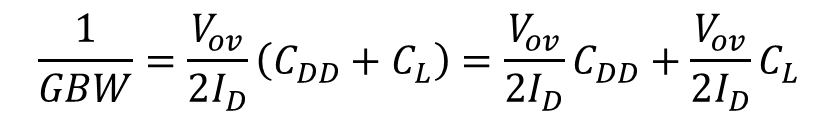

유도를 하기 위해 GBW의 역수를 표현하면 아래와 같다.

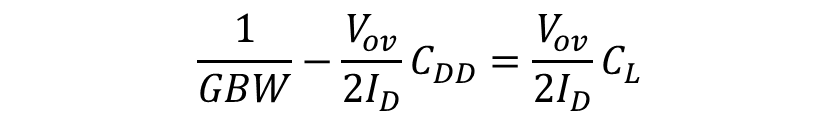

증명 3과 같이 정리하고 증명 1을 생각하여 정리하면 아래와 같이 Id에 관해 식을 쓸 수 있다.

분모 분자에 GBW/2를 곱해주면 아래 Id에 대한 결과가 나오게 된다.

부록 1. 식 6의 분모항(1-GBW*CDD/gm)

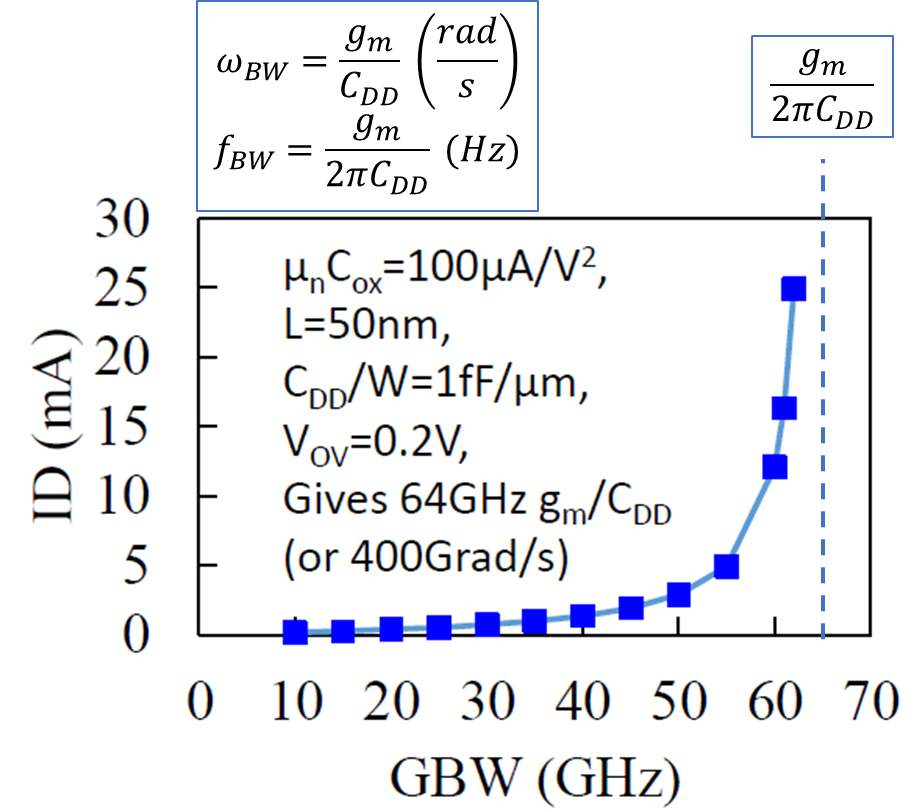

식 6을 통해 알 수 있었던 점은 GBW*CDD/gm=1이 되는 경우 드레인 전류(id)가 무한대로 폭팔하듯이 상승한다는 것이다.

다시 말해서 GBW가 gm/Cdd와 같아지는 지점이 된다면 드레인 전류는 급격하게 상승할 것을 의미한다.

그 다음으로 gm/CDD는 공정에 의존하는 파라미터임을 알 수 있다.

따라서 아래와 같이 표현이 가능하다

gm/W는 트랜스컨덕턴스 PER 폭이며 CDD/W는 기생 드레인 커패시턴스 PER 폭이다. 전자는 클수록 좋고, 후자는 작을수록 좋다.(대게 CDD/W= 1 ~ 2 fF/um 이다.)

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 잡음 전력 계산 (0) | 2021.12.07 |

|---|---|

| 회로 잡음 (Noise)과 전력 스펙트럼 밀도(power spectral density)의 이해 (4) | 2021.12.06 |

| 캐스코드 증폭기, 차동 증폭기 회로 주파수 응답 해석 (0) | 2021.11.26 |

| 공통 소스, 소스 폴로워, 공통 게이트의 주파수 응답(Frequency response of Common Source, Gate and Source Follower) (3) | 2021.11.23 |

| 캐스코드 전류 거울(Cascode Current Mirror) (2) | 2021.11.04 |

댓글