이 글은 피드백 회로의 12번째 진도이자 안정성 및 주파수 보상의 5번째 진도이다.

이전 진도와 동일하게 조금 더 어려운 내용들이 포함되어 있습니다. (생략 가능)

이전 진도

2022.01.26 - [전공(Major)/전자회로와 아날로그 회로설계] - 피드백 회로의 위상 마진(Phase Margin)

피드백 회로의 위상 마진(Phase Margin)

피드백회로 단원의 11번째 진도이자 및 주파수 보상 챕터의 네번째 진도이다. (이 글은 상급 내용도 다루고 있다. 이 둘의 내용에 대해서 구분선을 놓을테니 어려우면 읽지 않아도 좋다) 내용이

doctorinformationgs.tistory.com

주파수 보상(Frequency Compensation)

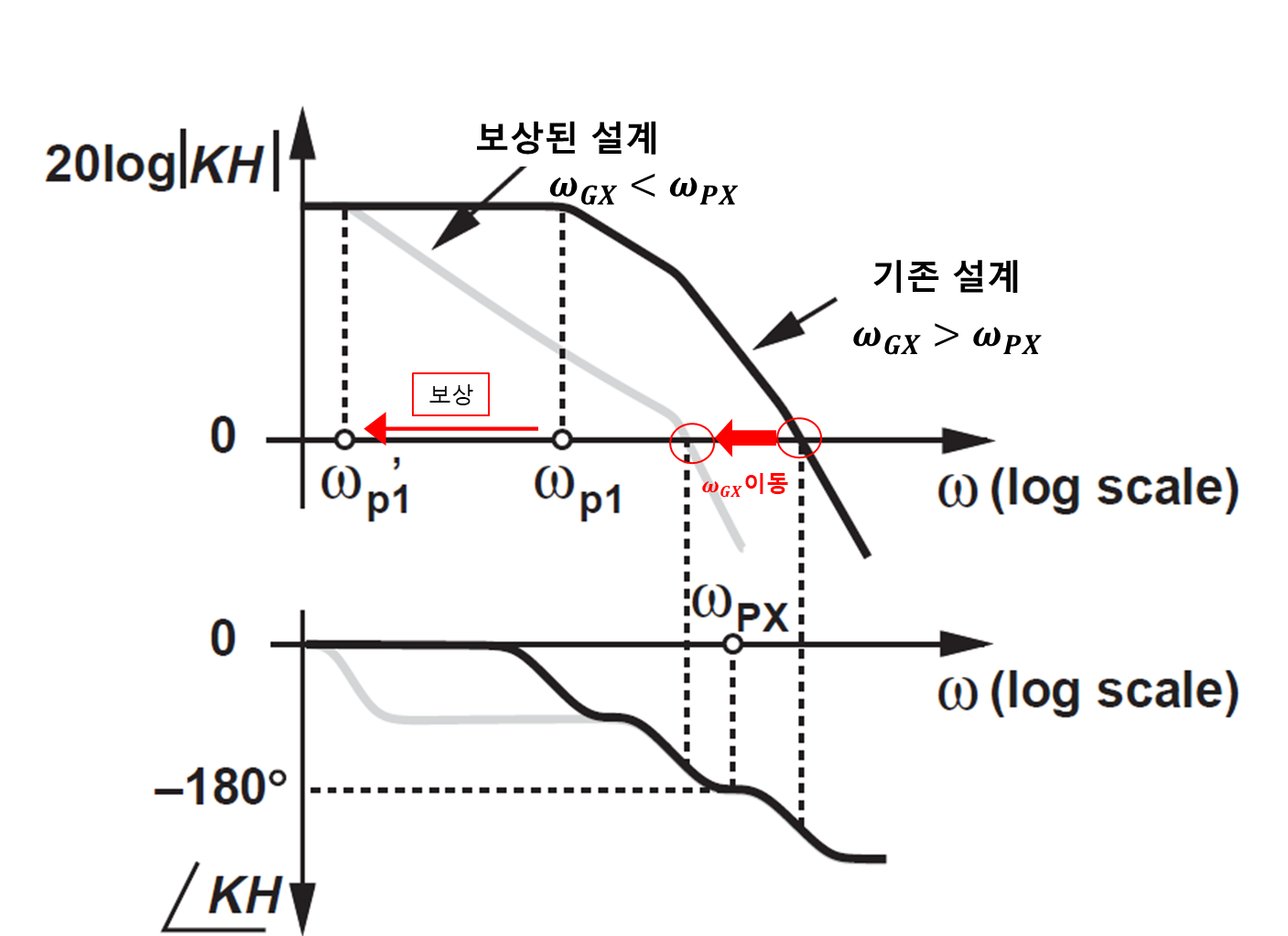

주파수 보상(Frequency Compensation)은 위상 교차 주파수(ωPX)를 변화시키지 않고 이득 교차 주파수(ωGX)를 원점 쪽으로 이동 시키는 것이다. 이는 그림 1을 통해 이해할 수 있다.

그림 1과 같이 낮은 주파수에서 루프이득이 1에 도달할 수 있게 기존의 극점(ωp1)에서 보완된 극점(ωp1')으로 주파수를 떨어뜨리면 위상 마진은 증가하게 된다.

주파수 보상을 위한 과정

그림 1을 다시 보도록 하자

기존 설계에서 위상 마진은 아래와 같다.

ωGX가 ωPX 보다 크기 때문에 시스템은 발진할 수 있다.

따라서 아래와 같은 과정을 거치게 되는데 식 1에서 <H(ωGX)를 변수로 두고 자신이 맞추고자 하는 위상 마진 값을 대입한다. 예로 45도 라고 하자 위상 마진이 45도가 되기 위해서는 <H(ωGX)가 <H(ω'GX)로 변수를 만들고 계산하게 되면 -135도를 가짐을 알 수 있다.

<H(ω'GX)는 -135도 임을 알 수 있고, 그림 1을 방금 언급한 예시를 따라 그려본다.

(1) <KH가 -135 지점에 수평선을 그린다.

(2) 회로의 위상 응답이 만나는 지점에서 수직으로 선을 그린다.

(3) 20dB/dec의 기울기를 갖는 선을 그린다.

(4) 20dB/dec의 기울기를 갖는 선과 낮은 주파수 이득이 만나는 지점은 보상된 극점이고 해당 극점을 표기한다.

(5) (4)를 토대로 위상의 변화를 그린다.

적당한 마진을 위해 두번 째 극점 밑에 있어야 하기 때문에 20dB/dec의 기울기를 가져야 한다는 것을 잊지말라.

(전자회로 2과정은 여기까지만 읽어도 좋다)

(조금 더 어려운 내용 생략 가능)

주파수 보상기법에 대한 문제

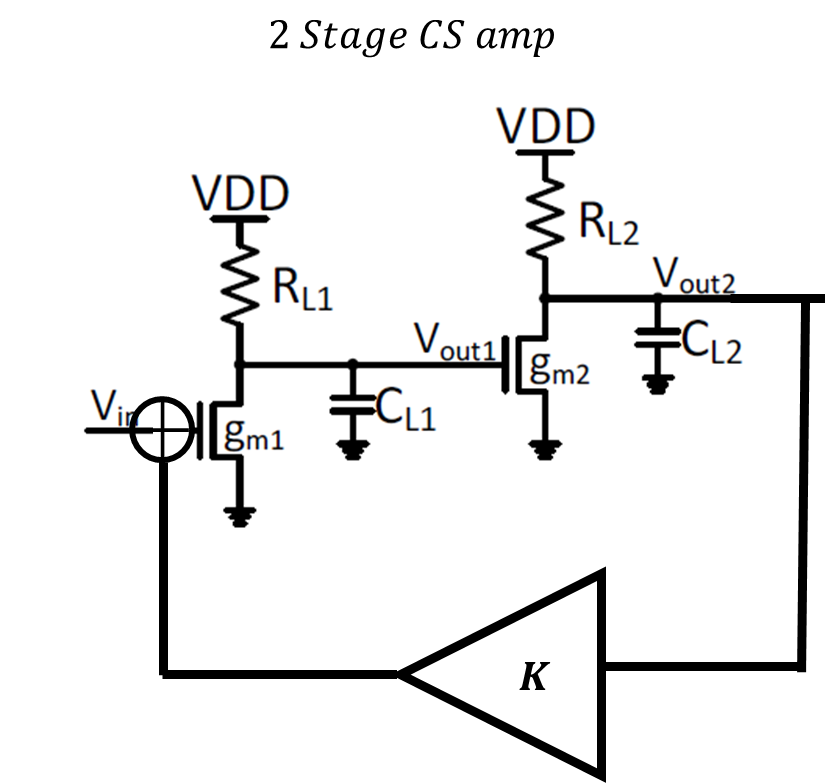

2 Stage OP Amp

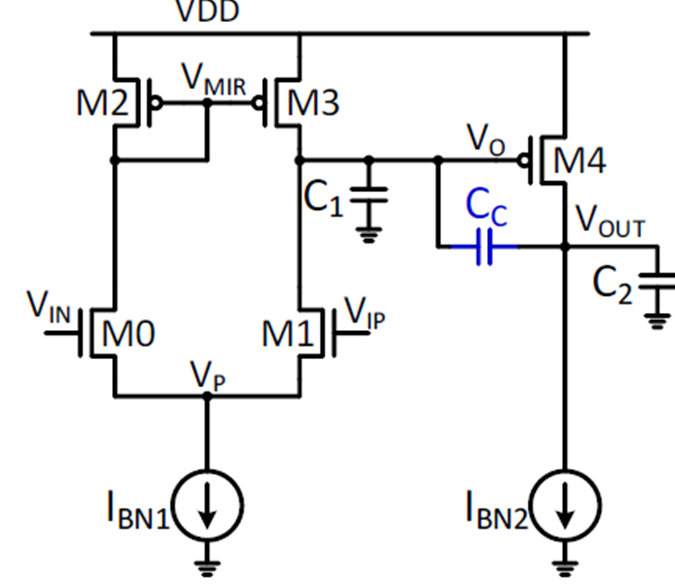

그림 3과 같은 회로를 해석해보자

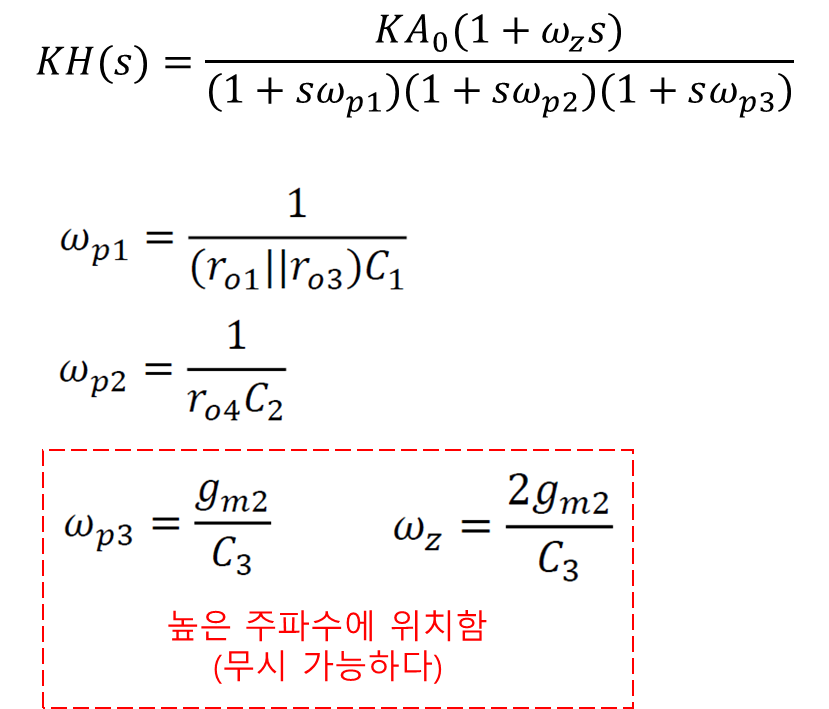

그림 9에서 보여주는 회로는 식 3과 같이 루프이득, 극점과 영점을 표현해줄 수 있다.

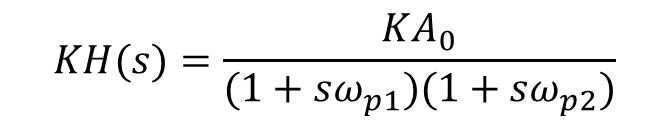

ro는 대게 큰 값을 가짐으로 식 3은 아래와 같이 간단하게 표현이 가능하다.

2022.01.26 - [전공(Major)/전자회로와 아날로그 회로설계] - 피드백 회로의 위상 마진(Phase Margin)

피드백 회로의 위상 마진(Phase Margin)

피드백회로 단원의 11번째 진도이자 및 주파수 보상 챕터의 네번째 진도이다. (이 글은 상급 내용도 다루고 있다. 이 둘의 내용에 대해서 구분선을 놓을테니 어려우면 읽지 않아도 좋다) 내용이

doctorinformationgs.tistory.com

다음 내용을 이해하기 위해 이전 진도에서 다루었던 두 조건들인 PM=45 or 60 에 따라 CL값을 고려하는 방법을 다시 한번 보는걸 권장한다.

그림 3 주파수에 따른 이득의 변화는 아래 그림 4와 같이 표현된다.

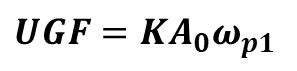

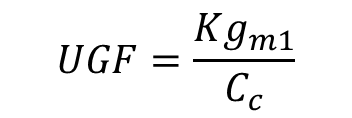

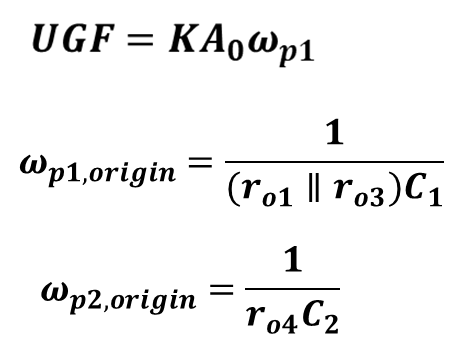

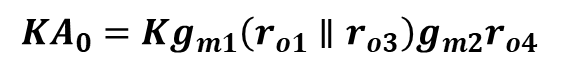

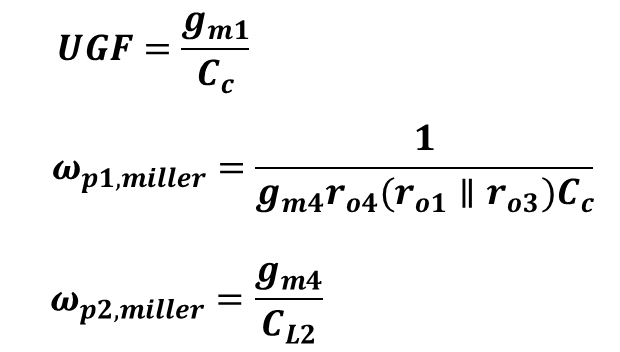

그림 3의 UGF는 아래와 같다.

45도의 Phase Margin인 경우 UGF가 두번째 극점의 위치에서 같거나 작아야 한다. 이를 수식으로 표현하면 아래와 같다.

설계를 위해 첫번째 극점의 C1은 C*1이 된다 왜냐하면 식 6과 같이 해당 위상 마진을 위해 추가 Cap을 달아야 할 수 있기 때문이다 따라서 식 3을 식 6에 대입하고 C1->C1*로 풀게 되면 아래와 같다.

밀러 보상(Miller Compensation)

밀러 이론의 기억이 까마득하다면 아래 링크를 통해 읽는 것도 좋다.

2021.09.15 - [전공(Major)/전자회로와 아날로그 회로설계] - 밀러 이론(Miller Theorem)

밀러 이론(Miller Theorem)

밀러 효과 하나의 부유(Floating) 임피던스를 2개의 접지된 임피던스들로 변환 시키는 방법이며, 부유 임피던스가 커패시터인 경우 각 노드에 하나의 극점을 연관시키도록 변환하는 방법이다. 이

doctorinformationgs.tistory.com

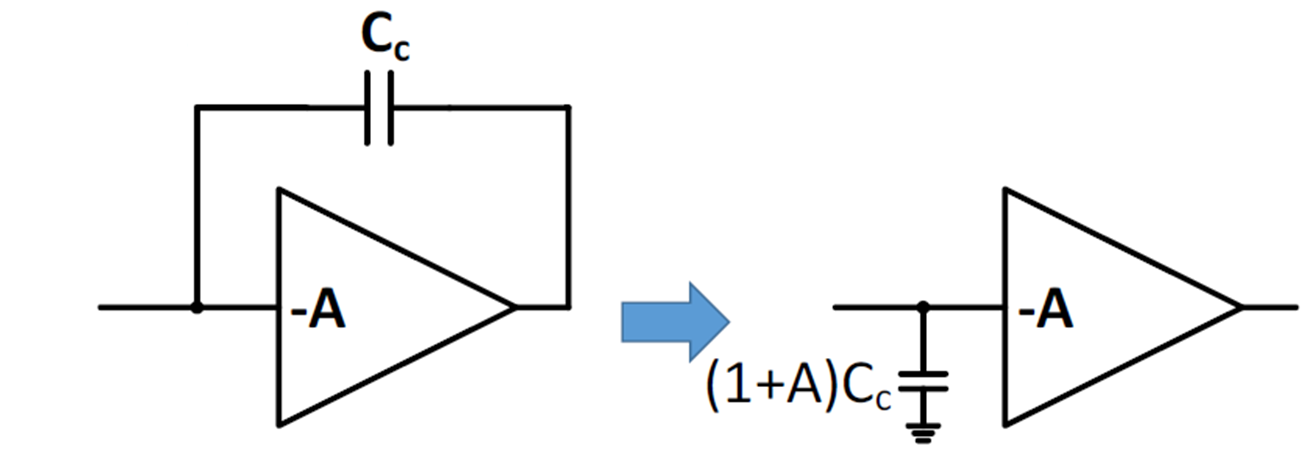

이해를 돕기 위해 그림 5를 보도록 한다.

밀러 이론은 증폭기 입출력 노드와 병렬로 Cc를 연결해줌으로써 큰 커패시턴스를 가질 수 있다.(밀러 이론)

밀러 이론은 주파수 보상을 위한 기법으로 아주 유용하며, 큰 커패시턴스는 보상을 위해 종종 요구된다.

극점 스플리팅(Pole splitting, 극점 나누기)로 불리는 또 다른 장점이 있다.

밀러 보상의 표준 구성(Canonical Configuration)

틀린 부분이 있을 수 있습니다. 틀린 부분에 대해 지적해주시면 바로 수정하도록 할게요

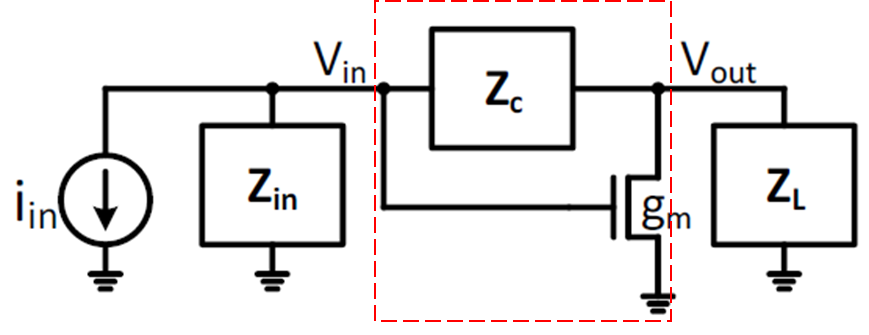

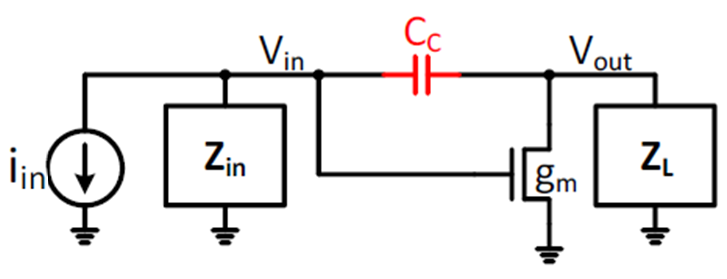

그림 6은 전형적인 밀러 보상의 구조를 보여준다.

밀러 이론을 통해 입출력 임피던스는 트랜스컨덕턴스 입출력 노드에 연결되어있는 Zc에 의해 영향을 받음을 알 수 있다.

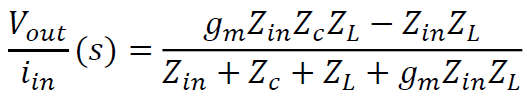

입출력 전달함수는 아래와 같다.

식 8에서 ZL은 로딩 R/C, Zin은 입력 R/C 임피던스이다.

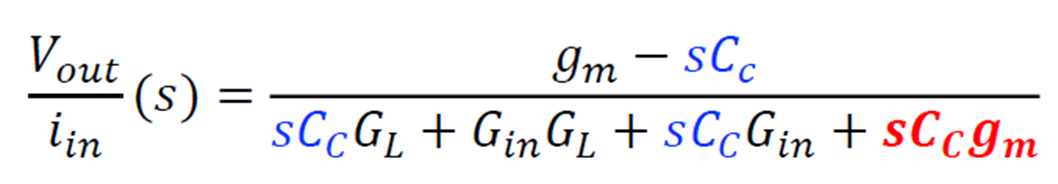

기본적으로 반환비율(Return-ratio) 해석으로부터 해당 표현을 식 8에서 얻을 수 있고 임피던스(Z)를 어드미턴스(G)로 바꿔주게 되면 식 9와 같이 표현이 가능하다.

밀러 보상은 대게 sC와 같은 커패시턴스 성분이기 때문에 어드미턴스 형식의 표현이 더 효율적이다.

만약 식 8 또는 9에서 피드백 임피던스가 0이라면 2개의 극점을 가지고 밀러 보상의 영향을 받지 않는다.

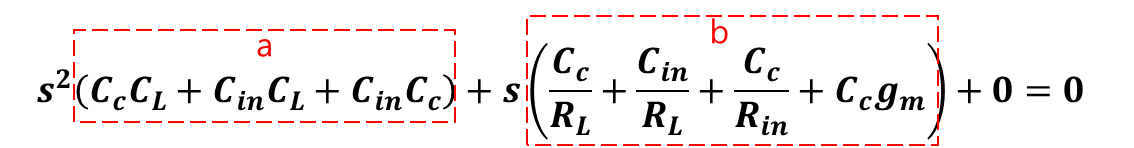

그림 6과 식 9을 학습하였고, 커패시터로 적용하면 아래와 같다.

식 9는 아래와 같이 수정이 가능하다.

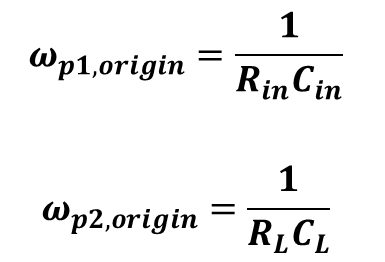

이제 극점이 어떻게 바뀌어지는지 보도록 하자.

밀러 보상이 없을때의 극점은 식 11과 주어진다.

밀러 보상이 있을 때 어떻게 변하는지에 대해 알아보도록 한다.

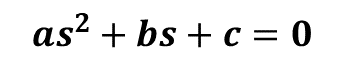

식 9의 분모는 식 12와 같이 전개가 될 수 있는데 분모항을 전개하면 아래와 같다.

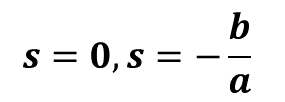

식 13을 통해 s는 아래와 같이 나온다

이는 낮은 주파수, 높은 주파수에 위치한 두개의 극점이 있다는 것을 알려준다.

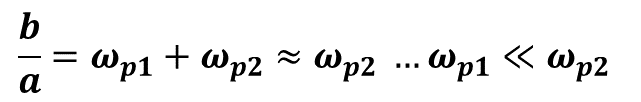

식 14를 극점에 대해 표현하면 아래와 같다

식 15에서는 첫 번째 극점이 우성 극점(dominant pole)임을 알려준다.

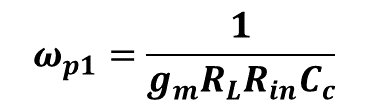

식 14를 통해 첫번째 극점을 알 수 없으므로 식 11 기존의 첫번째 극점을 통해 계산하게 되는데 밀러 이론으로부터 저주파 이득을 포함함을 다시 상기시키며, 저주파이득은 gmRL이다. 따라서 첫번째 극점은 아래와 같다.

식 16으로 부터 커패시터는 입력 Cin과 밀러 캡이 병렬로 연결되어 있고 대게 Cin은 작은 값으로 가정하여 얻은 결과이다.

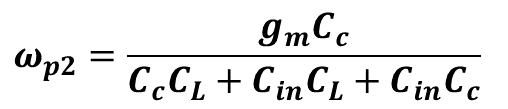

두번째 극점은 식 15를 통해 알 수 있다. a와 b를 식 13으로 부터 얻었고 이를 식 15에 대입하면 아래와 같다.

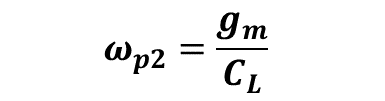

위에서 언급했듯이 입력 캐패시턴스는 낮은 값이고, 출력 임피던스는 밀러 이론으로부터 (1+A)배 낮추어 짐을 상기하여 계산하면 아래와 같이 간략화할 수 있다.

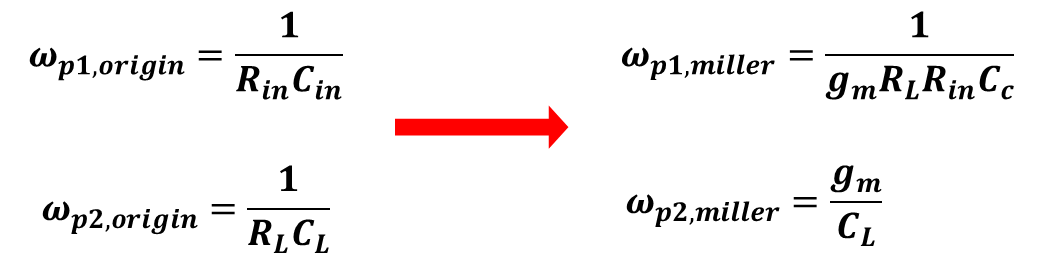

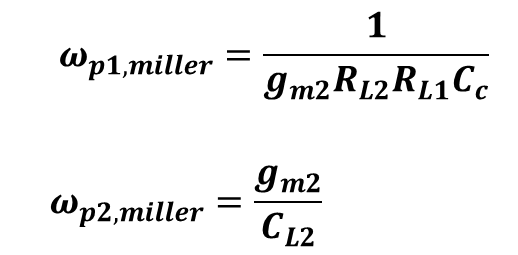

다시 기존 설계와 밀러 보상을 해준 극점의 변화에 대해 정리하면 아래와 같다.

정리하자면 밀러 보상을 통해 우성 극점(Dominant pole)은 더 낮은 주파수로 이동되고, 두번째 극점은 더 높은 주파수로 이동함을 알 수 있다. 이는 그림 1을 다시 확인 함으로써 우리가 왜 이런 기법을 하는지에 대해 다시 상기시킬 수 있다.

이전 진도에서 다루었던 두 예제들을 보도록 하자.

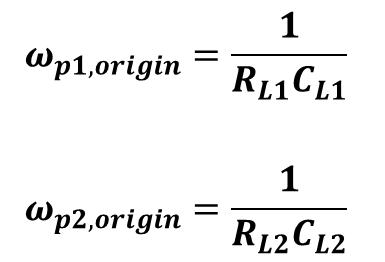

그림 8에서 보여준 예제는 밀러 캡이 없는 경우 극점은 아래와 같다. (ωp1<ωp2)

그리고 UGF는 기존에 구한 값과 동일하다.

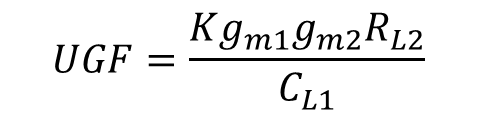

밀러 Cap을 Vout1, Vout2 사이에 연결 시켰을 때 극점은 아래와 같다.

식 22에서의 이득은 M2의 이득인 gm2RL2이며 Rin은 첫째단 부하저항이다.

UGF는 ωp1<ωp2 이므로 낮은 주파수 이득과 우성 극점(dominant pole)인 첫번째 극점과의 곱으로 나옴으로 아래와 같이 변경된다.

이를 통해 해당 예제는 간접적으로 UGF와 전력에 영향을 준다 왜냐하면 UGF보다 두번째 극점이 커야하기 때문에 gm2를 키워야 하는데 이는 드레인 전류의 증가를 야기한다.

2 stage OP Amp 예제를 다시 보도록 하자

그림 9에서 밀러 캡이 없는 경우의 UGF 및 극점은 아래와 같다. 식 5로 부터 볼 수 있지만 올려다보기 귀찮으니 다시 적어본다.

밀러 캡이 포함된 루프이득과 UGF 및 극점들은 아래와 같이 변경된다.

2 stage OP amp 또한 간접적으로 UGF와 전력에 영향을 준다 왜냐하면 UGF보다 두번째 극점이 커야하기 때문에 gm2를 키워야 하는데 이는 드레인 전류의 증가를 야기한다.

여러 보상 기법은 논문 또는 다른 관련 교과서에 있다. 다른 부분은 논문을 읽거나 책 또는 해외 강의 자료들을 찾아서 읽어보길 바란다.

전자회로 2 과정을 학습하셨습니다.

아래 링크를 통해 다음 진도와 전자회로 2의 모든 내용을 확인하실 수 있습니다.

2022.01.12 - [전공(Major)/전자회로 2 과정] - 전자회로 2 커리큘럼

전자회로 2 커리큘럼

전자회로 2 커리큘럼입니다. 전자회로 2에 대한 간략한 설명은 아래와 같습니다. 전자회로 1에서 배웠던 능동소자(Diode, BJT, MOSFET)에 대해 학습했으며 그에 대한 다이오드 회로 및 단일 증폭기인

doctorinformationgs.tistory.com

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 바이어스(Bias)의 의미와 PN 접합의 평형 상태, 순방향 바이어스, 역방향 바이어스에 대해 알아보자 (0) | 2022.02.11 |

|---|---|

| 드리프트(Drift), 확산(Diffusion), 전류밀도(Current Density)에 대해 알아보자 - 전자회로 기초 (0) | 2022.01.28 |

| 피드백 회로의 위상 마진(Phase Margin) (0) | 2022.01.26 |

| 진성(고유,intrinsic) 반도체와 외부(외인성, extrinsic) 반도체에 대해 알아보자 (0) | 2022.01.25 |

| 피드백 회로의 안정조건(Stability Condition of Feedback circuit) (2) | 2022.01.24 |

댓글