콜피츠 발진기는 단일 트랜지스터로 구성하여 발진을 형성할 수 있다. 다만 이는 여러가지의 트레이드 오프를 가져온다.

3점 발진기 (Three-Point Oscillator)

3점 발진기에서 알 수 있는 것은 콜피츠 발진기와 클랩 발진기에 대해 대략적으로 알 수 있다.

2022.05.05 - [회로 관련 전공/회로 과정 통합 글] - 음의 저항(Negative Resistance)과 1-단자 관점에서의 발진기

음의 저항(Negative Resistance)과 1-단자 관점에서의 발진기

이 글은 LC 발진기의 기초적인 내용을 다루고 있다. 이전 진도 2022.04.05 - [회로 관련 전공/회로 과정 통합 글] - 병렬 LC 탱크(Parallel LC Tank)와 손실 탱크(Lossy Tank) 병렬 LC 탱크(Parallel LC Tank)와..

doctorinformationgs.tistory.com

위 내용을 읽고 넘어가야 완만한 이해가 가능할 것으로 예상된다.

복습 1에 보이는 회로에서 발진기를 만들 수 있게 만드려면 노드 X, Y 사이에 인덕터를 연결하면 만들 수 있음을 지난 교차 결합 발진기에서 알 수 있었다. 그리고 이전 링크를 통해서 알 수 있는 중요한 발진 주파수에 대해서는 아래와 같이 정리가 되었다.

그리고 gmRp에 대해서는 아래와 같이 언급했었다.

C1=C2 일때 회로가 발진하려고 한다면

따라서 발진을 하려면 4 이상의 루프 이득이 필요함을 알 수 있다.

이전 포스팅(교차 결합 발진기)에서는 gmRp가 1 이상이면 발진 할 수 있었다. 이는 CMOS 공정에서 낮은 Quality Factor (Q) 값을 가지게 된다면 심각한 문제를 가져오는 점을 알 수 있다.

아래 세가지 방법으로 트랜지스터의 단자를 접지하여 각기 다른 모습의 발진기 구조을 알 수 있다. 이는 아래와 같다.

1) 소스 접지 (Source Grounded)

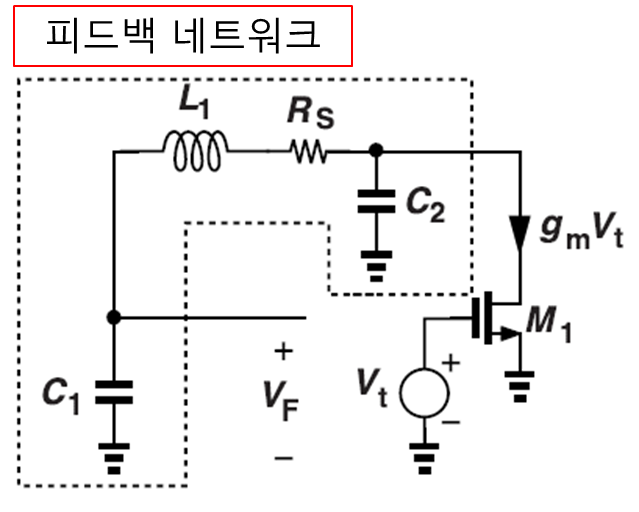

그림 1은 소스 접지 발진기를 보여준다.

그림 1의 소스 접지가 어떻게 발진 할 수 있는지는 지난 피드백 단원에서 루프 이득을 해석했던 절차를 이용해 알 수 있다.

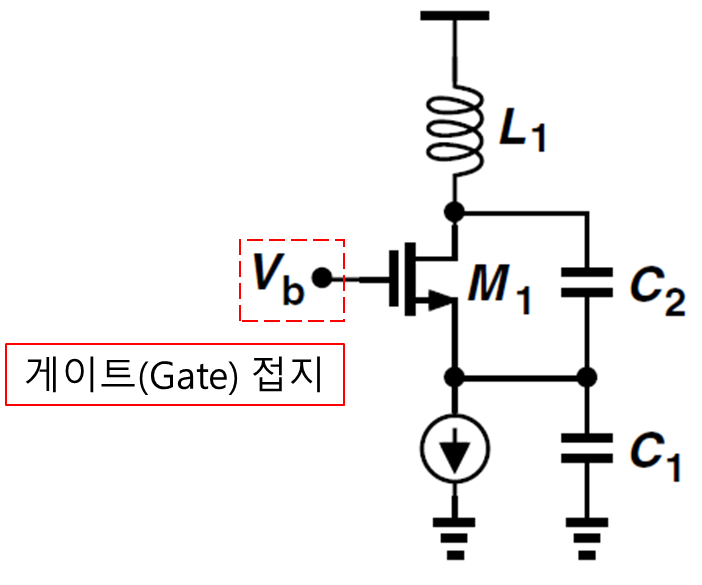

처음 언급 했던 복습 링크에서의 Rs는 아래와 같음을 언급했고, 발진 주파수 또한 복습 식 1과 동일하게 나온다.

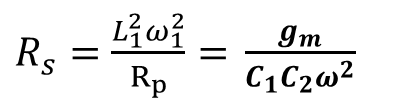

2) 콜피츠 발진기(게이트 접지, Gate-Grounded)

게이트 접지의 의미는 바이어스 전압 (Vb)이 인가되고 있으며 이는 소신호 해석에서는 ac 접지가 된다.

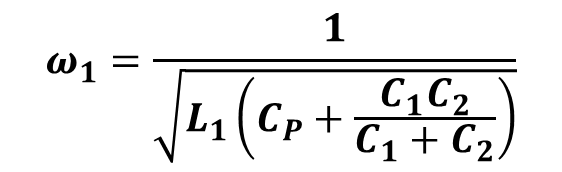

L1에 기생성분인 Rp, Cp가 있음을 알 수 있고 이에 대해 발진 주파수는 아래와 같이 표현할 수 있다.

루프 이득의 발진 조건은 복습 식 3과 같다.

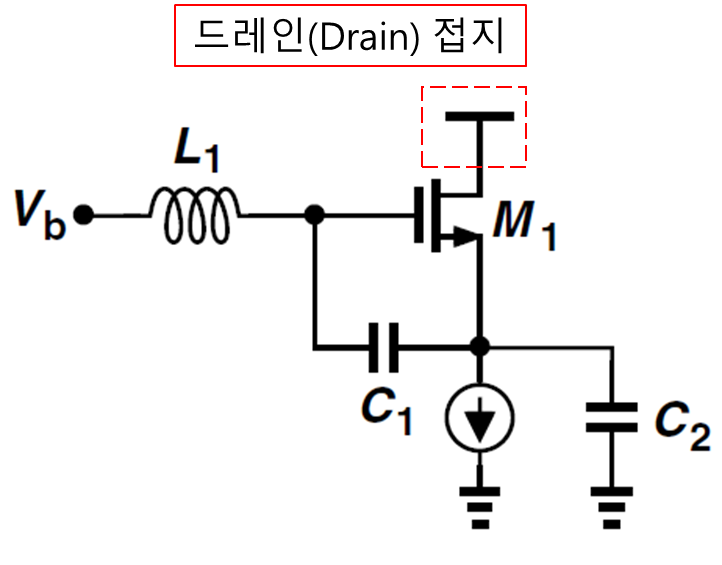

3) 클랩(Clapp) 발진기(드레인 접지, Drain-Grounded)

클랩 발진기는 드레인 접지라고도 불리며 이는 VDD와 드레인이 연결 되어 있고 VDD는 소신호 관점에서 ac 접지임을 알 수 있다.

발진 조건, 발진 주파수는 복습 식 3, 복습 식 1, 식 2에서 알 수 있다.

감사의 글

소정의 지식을 쌓는데에 도움이 되셨다면 광고 클릭을 하여 불쌍한 대학원 노예에게 10원의 기부를 부탁드립니다.

발진기, VCO와 PLL에 대한 통합 내용은

2022.03.08 - [회로 관련 전공/VCO(전압 제어 발진기)] - 전압 제어 발진기(VCO)에 대한 이론 정리

전압 제어 발진기(VCO)에 대한 이론 정리

1. 발진에 대한 개념 잡기 2022.01.19 - [회로 관련 전공/회로 과정 통합 글] - 보데의 법칙을 통해 회로의 전달함수H(s), 극점(pole), 영점(zero), 위상(Phase)을 알아보자 보데의 법칙을 통해 회로의 전달함

doctorinformationgs.tistory.com

발진기에 대한 내용은

아래 링크를 통해 다음 진도와 전자회로 2의 모든 내용을 확인하실 수 있습니다.

2022.01.12 - [전공(Major)/전자회로 2 과정] - 전자회로 2 커리큘럼

전자회로 2 커리큘럼

전자회로 2 커리큘럼입니다. 전자회로 2에 대한 간략한 설명은 아래와 같습니다. 전자회로 1에서 배웠던 능동소자(Diode, BJT, MOSFET)에 대해 학습했으며 그에 대한 다이오드 회로 및 단일 증폭기인

doctorinformationgs.tistory.com

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 플리커 잡음(Flicker Noise)에 대해 알아보자 (1) | 2022.07.05 |

|---|---|

| 전압제어 발진기(Voltage-Controlled Oscillator, VCO)에 대해 (3) | 2022.06.27 |

| 교차-결합 발진기 (Cross-Coupled Oscillator) (12) | 2022.06.21 |

| MOS 소자의 커패시터 동작과 바랙터(Varactor) (0) | 2022.05.07 |

| 음의 저항(Negative Resistance)과 1-단자 관점에서의 발진기 (0) | 2022.05.05 |

댓글