위 글을 참고하면 이해하는데에 조금 더 도움이 될 수 있다.

2021.10.22 - [회로 관련 전공/회로 과정 통합 글] - MOSFET의 커패시턴스 성분을 알아보자

MOSFET의 커패시턴스 성분을 알아보자

낮은 주파수에서 MOSFET 회로 해석을 할 때는 MOSFET 내부에 있는 기생 커패시턴스값이 매우 작기 때문에 무시하고 넘어갔다. 주파수가 점점 올라가면서 기생 커패시턴스(Parasitic capacitance)가 mosfet

doctorinformationgs.tistory.com

MOS 소자의 커패시터 동작은 앞으로 전자회로 2 또는 VCO, PLL 설계에 있어 나오는 내용이다.

커패시터에 대한 간략한 이론과 MOS Cap을 알아보고, 버렉터를 알아보는 순서로 진행하도록 하겠다.

복습 : 커패시터에 대한 이론

일반적인 평판(Plate) 커패시터인 경우에 수식은 아래와 같다.

복습 식 1에서 ε은 유전율, A는 극판의 면적, d는 극판 사이의 간격이다. 복습 식 1을 통해 커패시턴스는 면적에 비례, 거리와 반비례 하는 특성을 가졌다.

MOS 소자의 커패시터(Capacitor) 동작

MOS의 Capacitor의 동작은 아래와 같은 구성으로 되어 있다.

그림 1의 NMOS Cap은 2단자(2-Terminal) 소자로 생각할 수 있음을 알 수 있다.

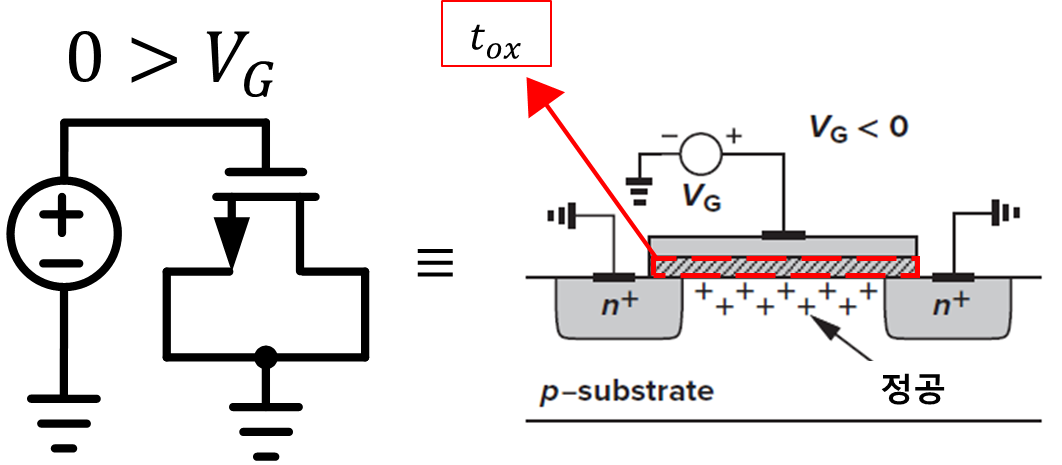

1) 게이트 전압이 매우 음수 일 때

매우 음수인 게이트 전압은 게이트에 (-) 전위(Potential)는 기판에 있는 정공을 산화막 경계면까지 끌어 당기게 됨으로NMOSFET는 축적 영역(Accumulation Region)에서 동작한다고 볼 수 있다.

2-단자 소자는 커패시터의 두 판(Plate)이 tox 만큼 떨어져 있음으로 Cox의 단위 면적 커패시턴스를 갖는 커패시터로 볼 수 있다. 여기서 Cox(산화물 용량)에 대해 식을 상기하자면 아래와 같다.

εox 는 SiO2의 유전율이고, tox는 산화물 두께이다.

2) 게이트 전압이 0에 가까울 때 (약 반전, Weak Inversion)

해당 내용은 MOS 물리에서 배웠던 내용과 비슷하다. 왜냐하면 게이트-소스 전압 (Vgs)가 증가함에 따라 정공의 밀도는 감소하게 되고 산화막 아래에 공핍영역이 형성되어 약 반전(Weak Inversion) 에 위치하게 된다.

이는 Cox와 Cdep와 직렬 연결로 볼 수 있고, Cap의 직렬 연결은 더 작은 Cgs 값을 가진다. 아래 그림 2와 같이 등가적으로 표현이 가능하다.

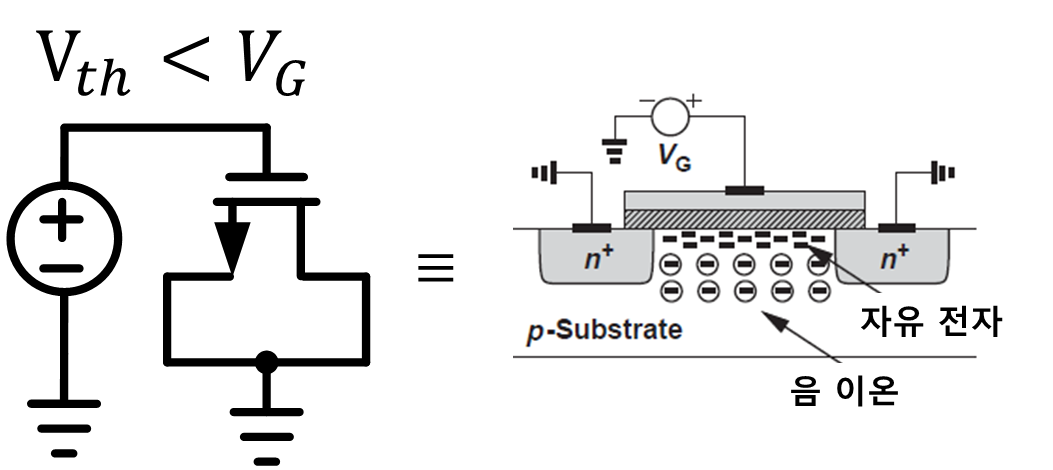

3) 게이트 전압이 약 반전 또는 문턱전압보다 클 때

Vgs 가 Vth보다 클 때 산화막-실리콘 경계는 채널을 형성, 단위 면적당 커패시턴스는 Cox로 돌아가게 된다. 이를 우리는 강 반전(Strong Inversion)이라 부른다.

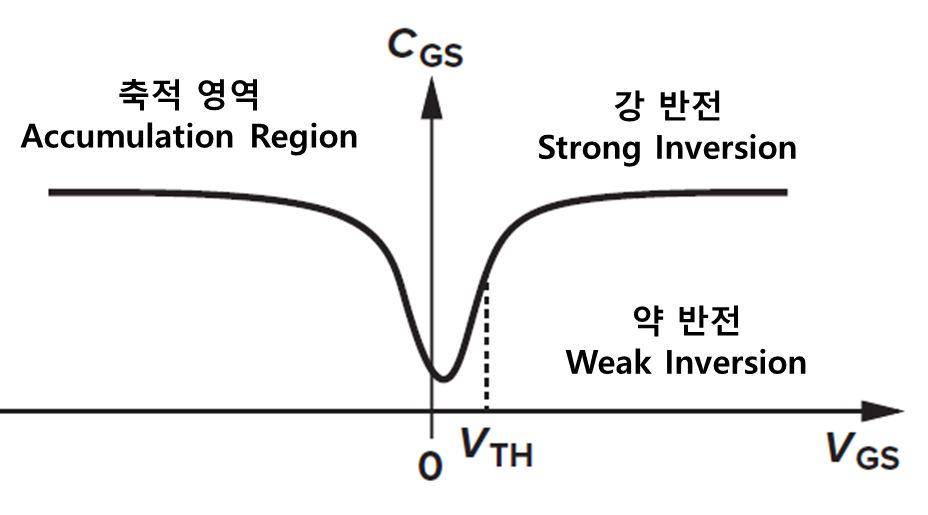

게이트-소스 전압(Vgs)의 변화에 따라 생기는 Cgs의 변화는 아래와 같으며 세 가지 영역을 정리하면 아래와 같다.

그림 5에서 커패시턴스-전압 특성은 비단조적(nonmonotonic) 증가를 보여주고 있는데 이는 VCO 설계에서 바람직하지 않다. 이는 VCO의 수학적 모델링에서 언급이 된다.

바랙터(Varactor, 버랙터)

현대 RFIC (Radio Frequency Integrated Circuits)에서 VCO 설계에서 MOS 바랙터를 사용한다.

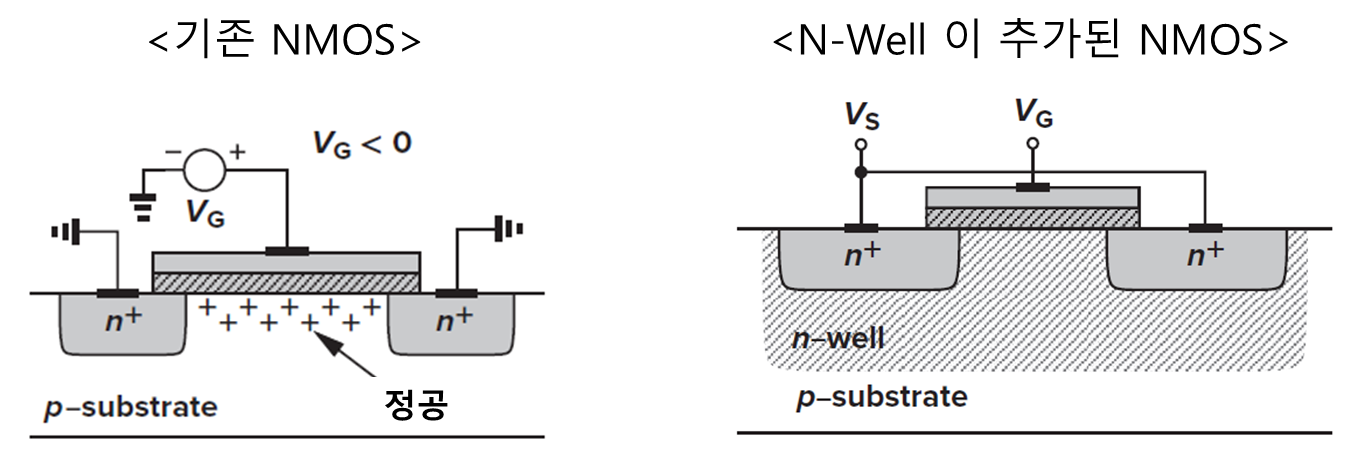

기존 MOS 커패시터의 비단조적인 이슈를 해결하기 위해서 n-well 안쪽에 NMOS 트랜지스터를 하나 만들어 축척모드 바랙터를 만들어준다. 이는 아래 그림 6에서 표현이 된다.

그림 6을 보게 되면 소스, 드레인 N-Well은 저항처럼 연결되어 있고 하나의 단자처럼 작동하며, 게이트는 다른 단자가 된다.

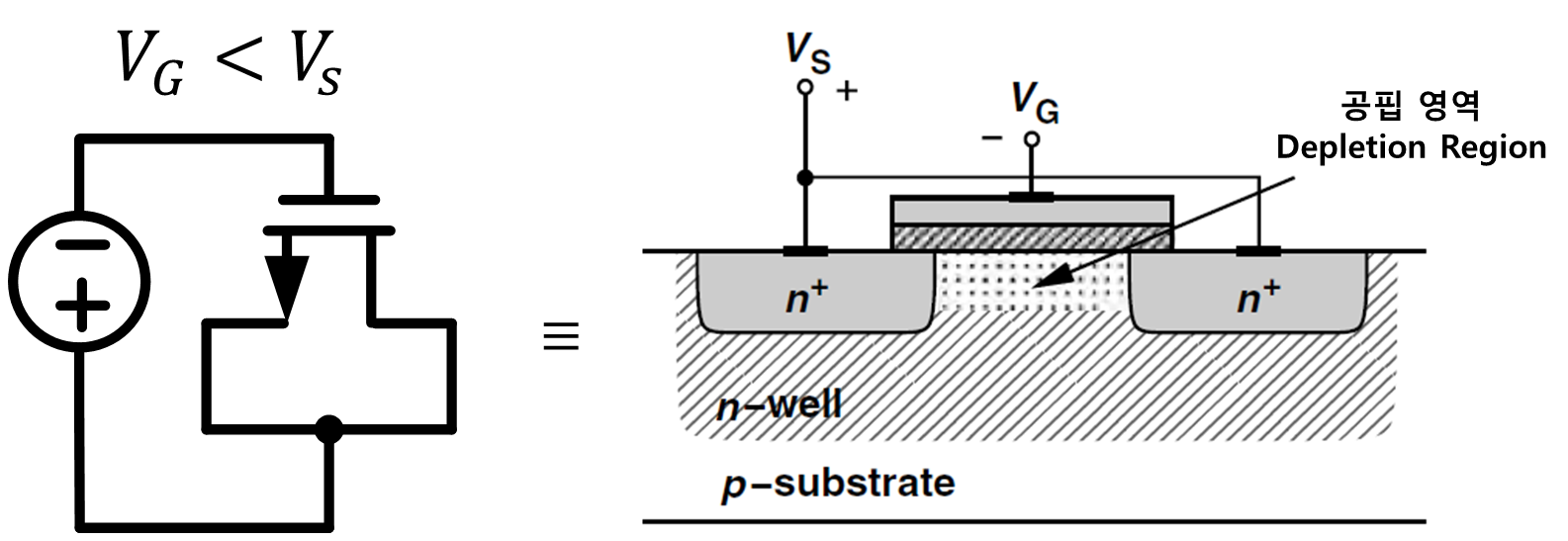

1) Vs > Vg 인경우

그림 7을 보게 되면 게이트 전압보다 소스 전압이 더 높은 것을 의미한다.

n-well의 전자는 실리콘-삼화막 경계면에서 밀려나고 공핍영역이 형성된다. 이는 위에서 언급한 NMOS 약 반전과 동일하게 되는데 Cox와 Cdep의 직렬 연결로 보기 때문에 작은 커패시턴스(Cmin)를 가지게 된다.

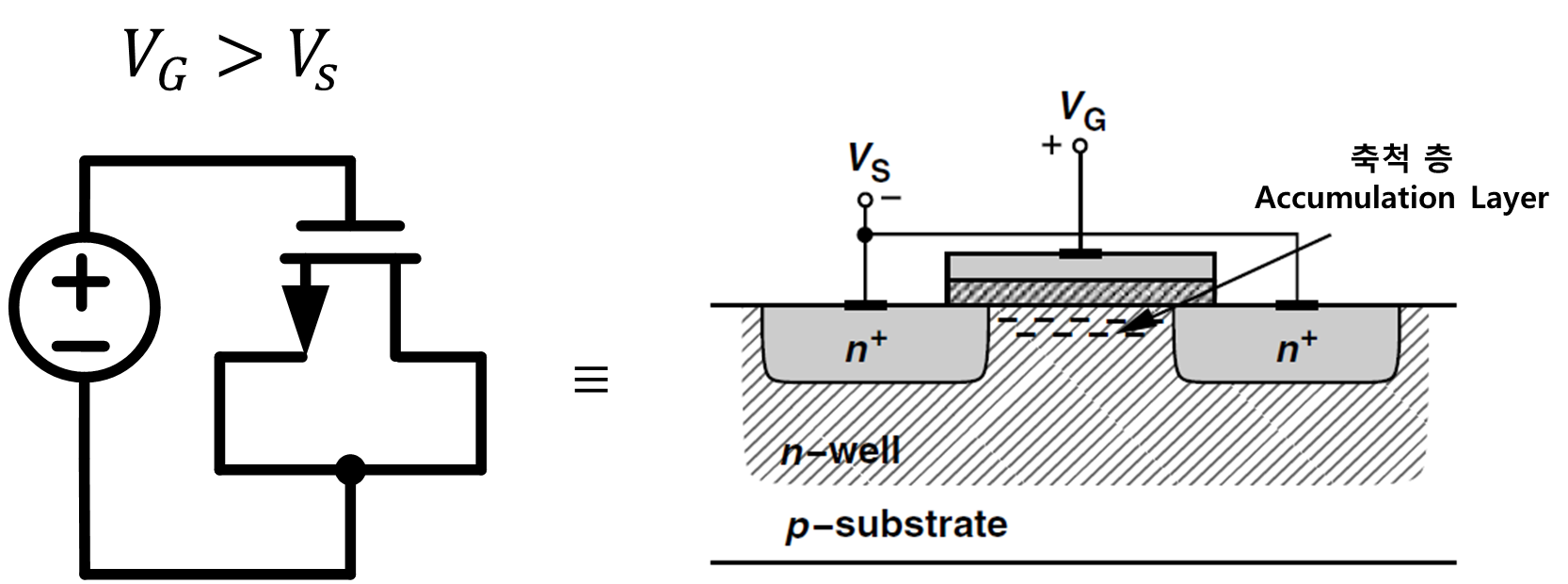

2) Vg > Vs 인 경우

강 반전과 동일하게 채널을 형성하고(게이트에 양이온이 있음으로) n-well에서는 전자를 끌어 당긴다. 따라서 전체 커패시턴스는 Cox(산화막 커패시턴스) 만큼 올라가게 되면서 제일 큰 커패시턴스 (Cmax)를 가지게 된다.

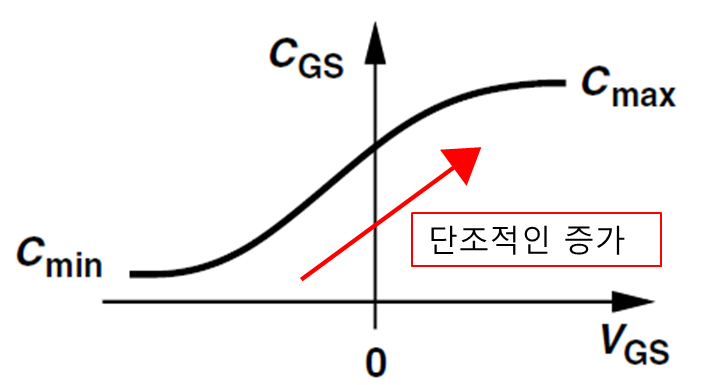

그림 5와 같이 커패시턴스-Vgs에 대한 특성을 도시하면 아래와 같이 표현이 가능하다.

그림 9를 통해 바랙터의 커패시턴스 특성은 Vgs에 따라 단조(monotonic)적인 증가 변화를 보여준다.

감사의 글

소정의 지식을 쌓는데에 도움이 되셨다면 광고 클릭을 하여 불쌍한 대학원 노예에게 10원의 기부를 부탁드립니다.

발진기, VCO와 PLL에 대한 통합 내용은

2022.03.08 - [회로 관련 전공/VCO(전압 제어 발진기)] - 전압 제어 발진기(VCO)에 대한 이론 정리

전압 제어 발진기(VCO)에 대한 이론 정리

1. 발진에 대한 개념 잡기 2022.01.19 - [회로 관련 전공/회로 과정 통합 글] - 보데의 법칙을 통해 회로의 전달함수H(s), 극점(pole), 영점(zero), 위상(Phase)을 알아보자 보데의 법칙을 통해 회로의 전달함

doctorinformationgs.tistory.com

발진기에 대한 내용은

아래 링크를 통해 다음 진도와 전자회로 2의 모든 내용을 확인하실 수 있습니다.

2022.01.12 - [전공(Major)/전자회로 2 과정] - 전자회로 2 커리큘럼

전자회로 2 커리큘럼

전자회로 2 커리큘럼입니다. 전자회로 2에 대한 간략한 설명은 아래와 같습니다. 전자회로 1에서 배웠던 능동소자(Diode, BJT, MOSFET)에 대해 학습했으며 그에 대한 다이오드 회로 및 단일 증폭기인

doctorinformationgs.tistory.com

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 콜피츠(Colpitts) 발진기와 클랩(Clapp) 발진기 그리고 3점 발진기에 대해 (0) | 2022.06.22 |

|---|---|

| 교차-결합 발진기 (Cross-Coupled Oscillator) (12) | 2022.06.21 |

| 음의 저항(Negative Resistance)과 1-단자 관점에서의 발진기 (0) | 2022.05.05 |

| 병렬 LC 탱크(Parallel LC Tank)와 손실 탱크(Lossy Tank) (0) | 2022.04.05 |

| 링 발진기(Ring oscillator) 기초 (0) | 2022.04.03 |

댓글