발진기를 배웠는데.. 결국엔 이 녀석이 하는것

1) 디지털 시스템을 위한 클럭 생성

2) 아날로그와 혼성 신호(Mixed-Signal) 시스템을 위한 클럭 생성

3) 무선 통신을 위한 반송 주파수(Carrier Frequency)

이 셋을 정리하자면 발진기는 결국 주파수 원(Frequency Source)를 만드는 것이고 어떤 System-On-Chip (SOC) 구조에서 만들어야 하는 필수적인 요소이다.

앞선 선행 과정에 대해서는

2022.03.08 - [회로 관련 전공/VCO, PLL] - 전압 제어 발진기(VCO)에 대한 이론 정리

전압 제어 발진기(VCO)에 대한 이론 정리

1. Oscillator(발진기)에 대해 알아보기 2022.03.11 - [회로 관련 전공/회로 과정 통합 글] - 발진기의 기본 개념(Basic Concepts of Oscillator) 발진기의 기본 개념(Basic Concepts of Oscillator) 발진기를 이..

doctorinformationgs.tistory.com

이 링크에 정리해두었다..

이제 VCO를 더 알아보도록 하자

전압제어 발진기(Voltage-Controlled Oscillator, VCO)

발진기는 주어진 특정 주파수 범위에 대해 튜닝을 하게 되며 주파수를 변화시킬 수 있는 발진기를 원하기 때문이다. 따라서 VCO가 이러한 역할을 하는 것이다. 이는 그림 1로 표현이 간단하게 표현이 가능하다.

Vcont가 VCO에 입력이 되고 이는 Vcont에 비례하여 ωout 또한 바뀜을 알 수 있다.

VCO 모델(VCO Models)

1) 출력 주파수가 관심있는 경우

출력주파수가 관심있는 경우 정적(Static) 시스템은 아래와 같은 특성을 가진다.

ω0는 세로축 상의 교차점 또는 Vcont=0 일 때의 절편을 나타낸다. Kvco는 회로의 이득(gain) 혹은 민감도(또는 감도, sensitivity)라 불린다. Kvco의 감도는 rad/Hz/V로 표현할 수 있고 이에 대한 VCO 특성은 그림 2로 표현 할 수 있다.

제어 전압(Vcont)가 V1 - V2로 변할 때 출력 각 주파수(ωout)는 ω1 - ω2 로 변하게 된다. 그림 2에서 ω2 - ω1를 튜닝 범위(Tunning Range)이다.

조금 더 설명하자면

식 1을 통해 알 수 있는점은 전압을 가변시키면 그에 상응하는 출력 주파수가 나옴을 알 수 있고 이는 비기억적(memoryless)임을 알 수 있다.

2) 출력 파형(waveform)이 관심있는 경우

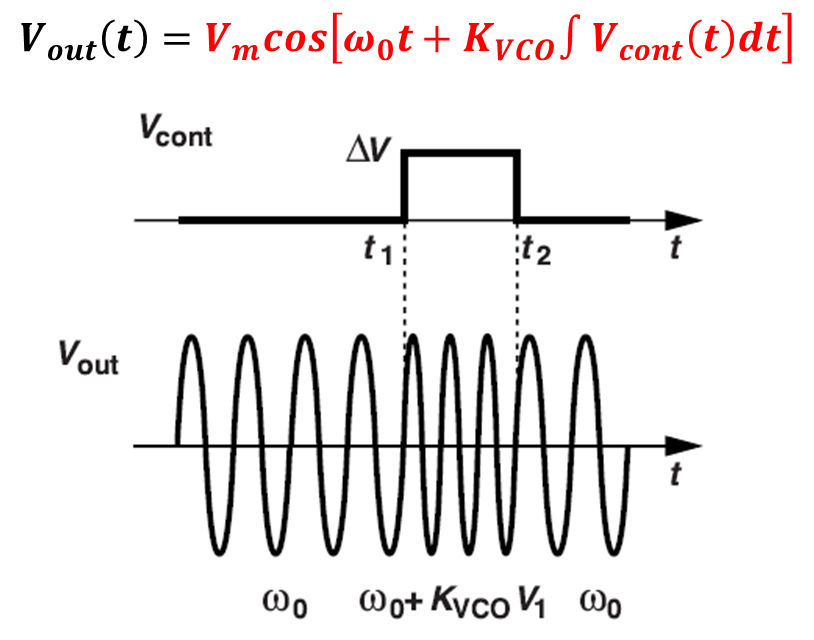

만약 출력 파형이 관심있는 경우 출력 전압은 아래와 같다.

위 식 2를 통해 알 수 있는 점은 VCO는 주파수 변조기(FM) 알 수 있으며 VCO와 PLL을 해석하는데에 필수적이다.

조금 더 보충설명 하자면

먼저 그림 3을 보도록 하자.

그림 3에서 어떤 신호는 π의 정수배가 될 때마다 출력전압(V0(t))이 0을 지나간다. 기울기는 ω0이며 위상(Phase)는 시간에 따라 선형적으로 변함을 알 수 있다.여기서 정현파, Vout(t)=Vm*cos(ωt) 이며 이 정현파의 위상각은 전체 위상이라 부른다.

여기서 ω0을 그냥 ω라고 생각하고, ωt=Φ(t) 이다. 시간에 따라 위상이 변한 것임을 알 수 있기 때문에

식 2-1 과 같이 정의가 된다. 그럼 Φ는 아래와 같다.

(중요치 않기 때문에) Φ0=0 이다. 출력 전압은

여기서 식 2-2와 ω에 대해서는 식 1과 같음으로 대입하게 되면

이는 식 2의 증명과정을 나타냈다. 그림 3에서 기울기가 더 높아진다면 더 높은 주파수에서 동작함을 알 수 있고, 기울기가 더 낮다면 더 낮은 주파수에서 동작함을 이해하고 넘어가도록 하자.

3) 이상적인 위상 적분기

이상적인 위상 적분기는 아래와 같이 특정할 수 있다.

여기서 Φex는 잉여 위상(excess phase)이다.

전달 함수인 식 3을 통해 알 수 있는 점은 제어전압(Vcont)과 잉여위상의 비는 하나의 적분기로 동작함을 알 수 있다.

조금 더 보충설명 하자면

식 2-4에서 빨간색으로 적힌 부분이 위상에서 관심사 항임을 알아야 한다.

Control 전압이 ∆V 만큼 증가했을 때를 고려해보자

∆V 만큼 증가하게 되면 그림 4에선 주파수에서 변조가 일어남을 알 수 있고 출력 주파수 ωout=ω0 -> ωout=ω1 으로 바뀌게 된다. 이는 그림 5에서 알 수 있다.

그림 6에서 전체 위상은 그림 5를 기반으로 도시화한 것이며, 이는 VCO의 위상의 변화는 과거의 값을 기억한다.(Remeber) 만약 ∆V만큼 증가하지 않고 출력 주파수가 ωout=ω0 였다면 ω0의 기울기를 가지고 전체 위상은 그림 3과 동일한 결과로 나왓을 것이다.(빨간색 투명선)

하지만 Vcont이 rise and fall을 경험했기 때문에 전체 위상은 과거의 ∆V만큼의 위상 변화만큼 바뀌었음을 알 수 있다.

그림 5와 6을 정리하게 되면 아래와 같이 볼 수 있다.

감사의 글

소정의 지식을 쌓는데에 도움이 되셨다면 광고 클릭을 하여 불쌍한 대학원 노예에게 10원의 기부를 부탁드립니다.

발진기, VCO와 PLL에 대한 통합 내용은

2022.03.08 - [회로 관련 전공/VCO(전압 제어 발진기)] - 전압 제어 발진기(VCO)에 대한 이론 정리

전압 제어 발진기(VCO)에 대한 이론 정리

1. 발진에 대한 개념 잡기 2022.01.19 - [회로 관련 전공/회로 과정 통합 글] - 보데의 법칙을 통해 회로의 전달함수H(s), 극점(pole), 영점(zero), 위상(Phase)을 알아보자 보데의 법칙을 통해 회로의 전달함

doctorinformationgs.tistory.com

발진기에 대한 내용은

아래 링크를 통해 다음 진도와 전자회로 2의 모든 내용을 확인하실 수 있습니다.

2022.01.12 - [전공(Major)/전자회로 2 과정] - 전자회로 2 커리큘럼

전자회로 2 커리큘럼

전자회로 2 커리큘럼입니다. 전자회로 2에 대한 간략한 설명은 아래와 같습니다. 전자회로 1에서 배웠던 능동소자(Diode, BJT, MOSFET)에 대해 학습했으며 그에 대한 다이오드 회로 및 단일 증폭기인

doctorinformationgs.tistory.com

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 지터(Jitter)와 위상 잡음(Phase Noise)의 기본 구성과 위상 잡음과 전력 사이의 Trade-OFF(상충 관계) (0) | 2022.07.08 |

|---|---|

| 플리커 잡음(Flicker Noise)에 대해 알아보자 (1) | 2022.07.05 |

| 콜피츠(Colpitts) 발진기와 클랩(Clapp) 발진기 그리고 3점 발진기에 대해 (0) | 2022.06.22 |

| 교차-결합 발진기 (Cross-Coupled Oscillator) (12) | 2022.06.21 |

| MOS 소자의 커패시터 동작과 바랙터(Varactor) (0) | 2022.05.07 |

댓글