본 포스팅은 op amp에서 다루는 비이상적인 효과인 slew rate에 대해 알아본다.

실험에서 설명하는 간단한 방법은 아래 링크에 언급해 놓았다.

2021.05.16 - [실험 관련/회로이론 실험] - Slew Rate란 무엇인가?

Slew Rate란 무엇인가?

이상적인 OP Amp는 어떤 입력신호에 대해서도 충실히 출력신호를 출력할 수 있지만, 실제로는 Slew Rate라는 제한이 존재합니다.OP Amp 출력신호 기울기의 최대치를 의미합니다.(아래 좌측 사진) 이로

doctorinformationgs.tistory.com

슬루율

(Slew Rate)

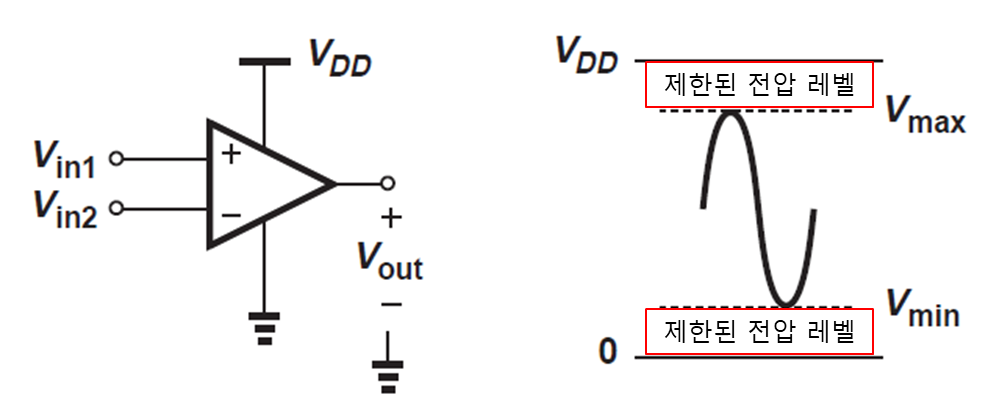

슬루율은 연산 증폭기의 대신호 동작에서 발생하는 문제점이다. 이해를 돕기 위해 아래 그림 1 전압 폴로워를 보도록 하자.

그림 1에서 전압 폴로워에 계단 함수의 입력을 인가하게 되면 출력 전압이 입력과 동일하게 계단 함수의 형태로 나와야 하지만 큰 입력의 계산 함수인 경우 연산 증폭기 내부 회로가 커패시터를 충전시키는 정정류원으로 바뀌기 때문에 파형의 경사로 부분이 증가하게 된다. 실제 op amp에서는 슬루율(Slew Rate, SR)에 해당하는 기울기로 linear하게 증가하는 ramp 함수로 나오게 된다.

이러한 결과로 연산 증폭기는 슬루잉(Slewing) 되었다거나 슬루율이 제한(slew rate limited)되었다고 표현한다.

이러한 현상은 왜 발생하는 것일까?

정답은 연산 증폭기 내부에 설계된 회로에 의해 발생하는 현상이다.

입력 신호인 계단 함수가 그림 1에서의 V 보다 작게 되면 출력은 아래와 같이 지수적으로 증가하는 ramp가 될 수 있다.

전압폴로워의 전달함수는 아래와 같은데

식 1에서 ωt는 단위 이득을 가질 때 주파수를 의미하고, 식 1의 시정수는 아래와 같다.

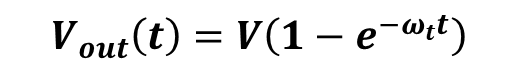

저역통과 단일 시정수 응답을 통해 출력 전압은 아래와 같다.

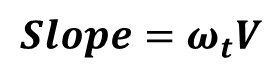

기울기를 구하기 위해서는 시간에 대해 식 3을 미분함을써 초기 기울기는 아래와 같다.

식 4를 통해 V의 level이 SR 이하여야 함을 알 수 있다.

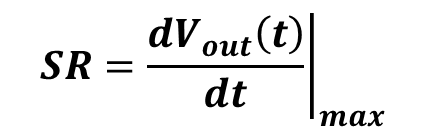

입력 전압 V의 level이 충분히 작은 경우(식 5를 만족하는 경우) 지수적으로 증가하는 출력 전압은 아래 그림 2로 도시화 할 수 있다.

위 내용들을 종합해 보았을 때 연산 증폭기(OP Amp) 출력 전압이 큰 신호가 나올 때, 비선형(nonlinearity) 왜곡(distortion)을 만드는 현상이며 슬루율은 실제 op amp가 따라갈 수 있는 출력 전압에 특정한 최대 변화율이 존재하고 이 최대값(maximim value)이다. 이는 아래와 같이 정의 할 수 있다.

식 6의 슬루율은 V/μs 의 단위를 가진다.

최대 전력 대역폭

(Full power bandwidth)

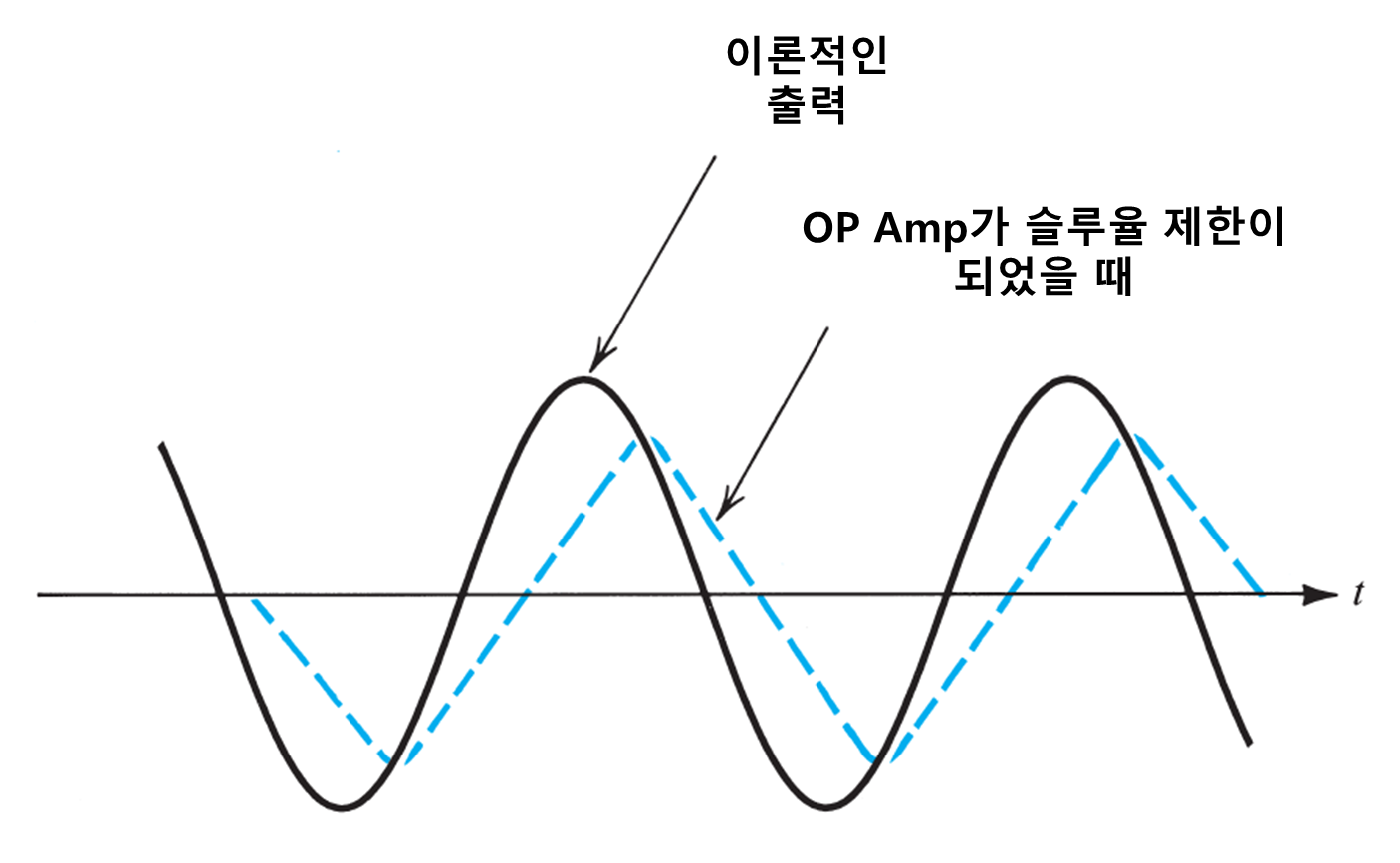

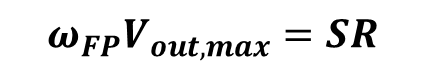

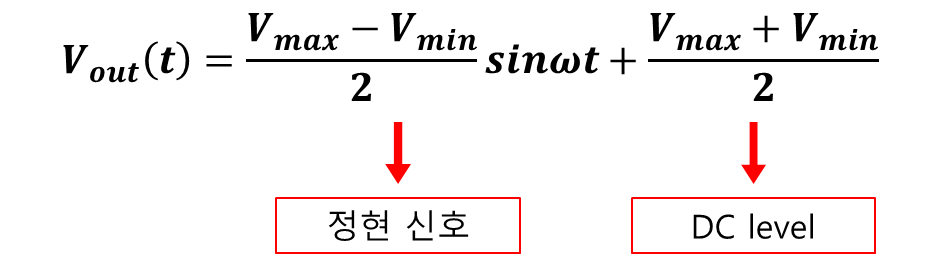

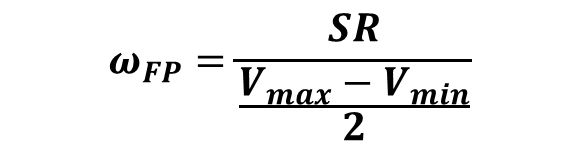

최대 전력 대역폭(f_FP)은 op amp의 정격 출력 전압과 동일한 크기의 진폭을 갖는 출력 사인파가 슬루율 제한에 의해 왜곡을 보이기 시작하는 주파수를 말한다. 어떤 출력 전압을 Vout,max 로 표현한다면 출력 사인파가 최대 전력 대역폭과 슬루율의 관계는 다음과 같이 표현이 가능하다.

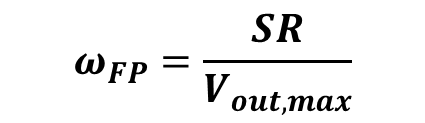

ω_FP에 대해 정리하면

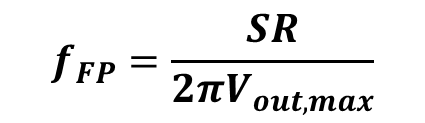

그리고 각주파수가 아닌 주파수에 대해 표현하면 아래와 같다.

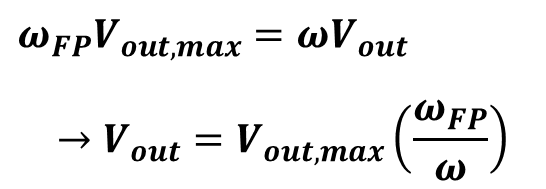

실제로 주파수가 ω인 출력 사인파가 왜곡되지 않게 하기 위한 최대 진폭에 대해서는 아래와 같다.

출력 전압을 알아보기 위해 아래 그림 4를 보도록 하자

그림 4의 op amp의 출력 전압은 op amp의 성능을 떨어뜨리지 않기 위해 제한되는 전압레벨을 제외한 나머지가 최대 출력 스윙의 폭이다. 조금 더 상급 교재에서 배우겠지만 해당 레벨을 넘어가게 된다면 op amp의 성능이 떨어진다.

출력에서 허용되는 가장 큰 정현파에 대해서는 아래와 같다.

식 10이 식9를 통해 진행된다면

가 된다. 최대 전력폭은 연산 증폭기의 유용한 대신호 속도의 척도를 제공한다.

전자회로 1 과정을 학습하셨습니다.

아래 링크를 통해 다음 진도와 전자회로 1의 모든 내용을 확인하실 수 있습니다.

2022.01.13 - [전공(Major)/전자회로 1 과정] - 전자회로 1 커리큘럼

전자회로 1 커리큘럼

전자회로 1 커리큘럼입니다. 기본적으로 반도체 공학에서 배웠던 능동소자(Diode, BJT, MOSFET)를 통해 단일 증폭기를 설계한다. 회로를 해석하는데에 있어 회로이론에서 배운 회로 해석기법을 사용

doctorinformationgs.tistory.com

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| BJT 바이어스 회로를 알아보자 (BJT bias circuits) (0) | 2023.03.24 |

|---|---|

| 회로 내에서의 잡음 표현 (0) | 2023.03.22 |

| 대수 증폭기(Logarithmic amplifier)와 제곱근 증폭기(Square-root Amplifier)에 대해 알아보자 (0) | 2023.03.19 |

| 정밀 정류기 (Precision Rectifier)에 대해 알아보자 (2) | 2023.03.18 |

| 능동 모드에서 동작하는 BJT에 대해 알아보자 (Active mode in BJT) (0) | 2023.03.16 |

댓글