해당 글은 공통 이미터 증폭기 포스팅에서 이어지는 글입니다.

공통 이미터 증폭기(Common-Emitter Amplifier)에 대해 알아보자(이미터 축퇴 공통 이미터 증폭기까지)

공통 이미터 (Common-Emitter) 공통 이미터 구조는 아래 그림 1과 같다. 공통 이미터(CE, Common-Emitter)는 입력을 베이스 단자에 인가하고 출력은 콜렉터 단자에서 나온다. 이미터가 공통 접지 되어 있기

doctorinformationgs.tistory.com

공통 베이스 증폭기

(CB Amp, Common-Base Amplifier)

공통 베이스 코어 (CB core)

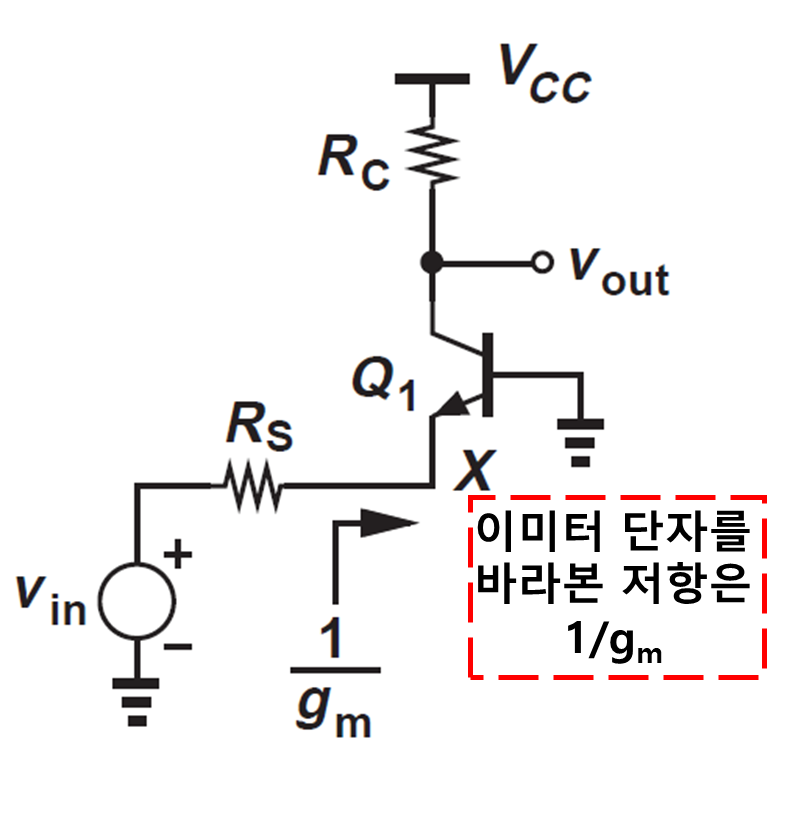

아래 그림 1은 공통 베이스 코어를 표현한 것이다.

공통 베이스는 베이스 단자 이미터 단자에서 입력을 감지하고 컬렉터 단자에서 출력이 나온다. 공통 이미터 증폭기와 다르게 공통 베이스는 입력에서 어떤 데이터 신호를 감지하면 동위상(In-Phase)으로 출력이 나온다. 해당 내용에 대해서는 t-domain에 언급하도록 한다.

t-domain 해석과 소신호 등가회로 해석

이미터에 인가되는 전압은 DC 성분이 없고 AC 성분만 있다고 가정하고 DC에서의 KVL을 인가하면 아래 식 1과 같이 나옴을 알 수 있다.

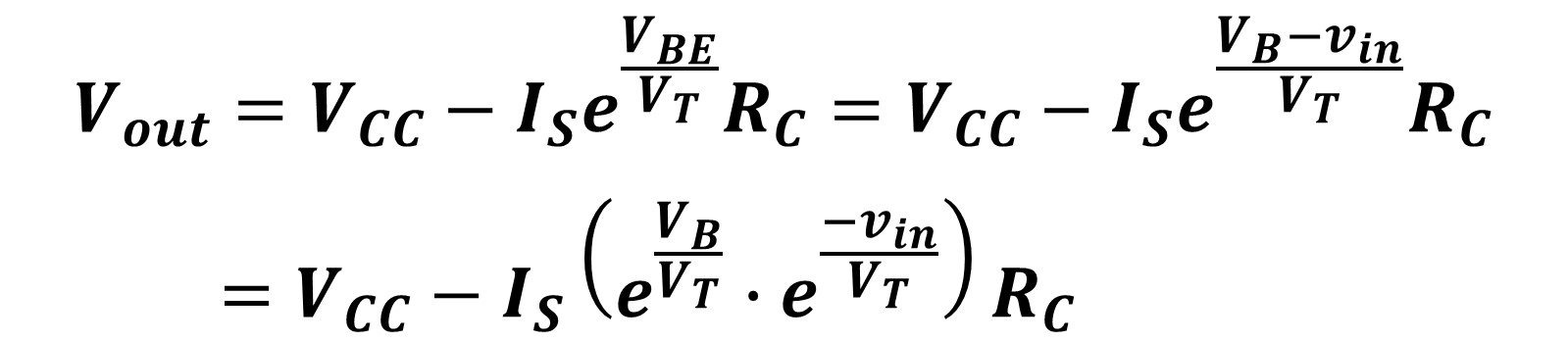

식 1에 대해 이미터 단자에서 어떤 신호의 변화를 감지 하는 경우에 출력 전압에 대해서는 아래 식 2와 같이 표현이 가능하다.

식 2에서 Vbe = Vb - Ve 전압인 것을 명심하도록 한다. 입력 신호 변화에 따른 출력 전압에 대해서는 아래와 같이 나온다.

식 3을 통해 알 수 있는 점은 이미터 단자에서 입력을 감지하다보니 이미터 전압의 상승은 컬렉터 전류(Ic)의 감소를 야기하고 이미터 전압의 감소는 컬렉터 전류(Ic)를 증가시킨다. 이로 인해 공통 이미터 증폭기와 달리 입력 신호와 출력 신호는 동위상을 갖게 된다는 것이다. 이제 소신호 등가회로를 통해 전압 이득을 확인해본다.

출력 노드에 KCL을 적용하여 나온 식은 아래 식 4와 같다.

식 4에서 vin의 부호에 대해서는 베이스-이미터-그라운드에서 KVL을 적용할 수 있다. 그리고 전압 이득에 대해서는

식 3과 동일함을 알 수 있다.

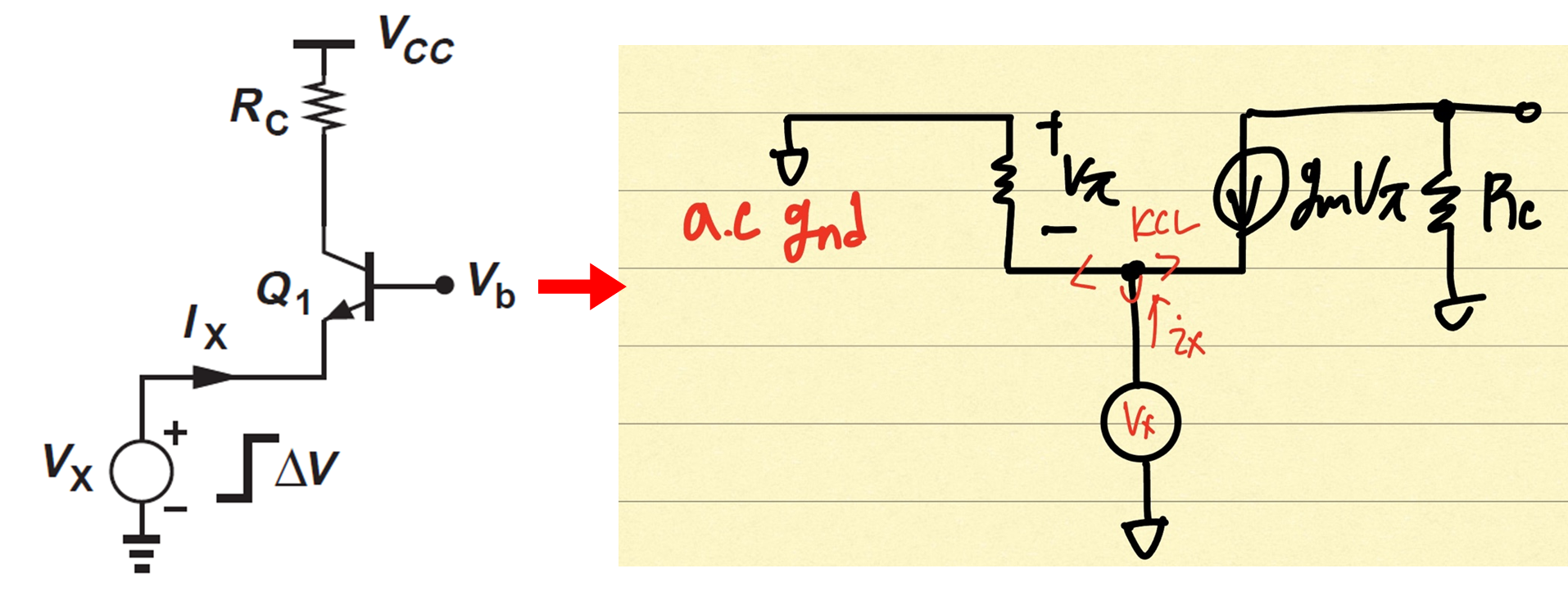

CB core의 입력 저항 또는 임피던스 [Input resistance (or impedance) of CB core]

아래 링크는 입력 저항에 대해 이해하는데에 있어 도움이 될 수 있습니다.

2021.10.07 - [회로 관련 전공/Basic] - 입출력 임피던스는 왜 필요할까?

입출력 임피던스는 왜 필요할까?

의문점 학부시절에서 어디에서 보는 임피던스를 항상 물어본 것이 기억이 난다. 회로이론에서는 어떤 두 노드에서 보이는 임피던스, 전자회로에서는 입력과 출력 임피던스를 항상 구하게 된다.

doctorinformationgs.tistory.com

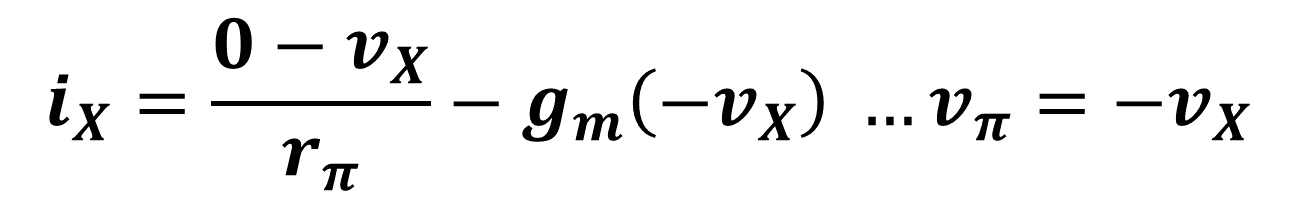

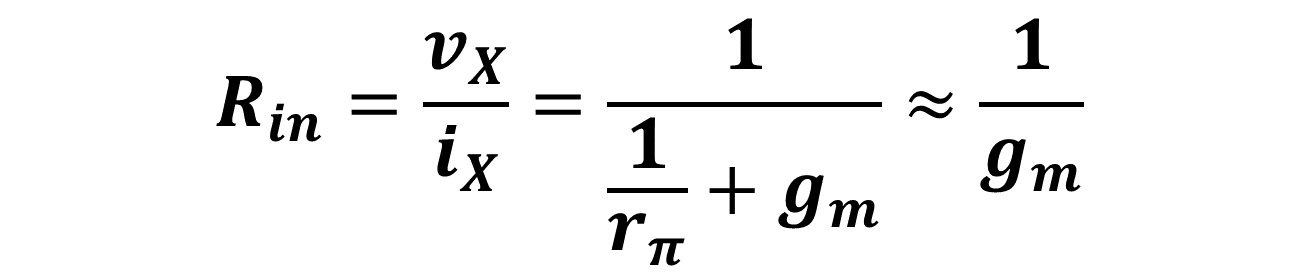

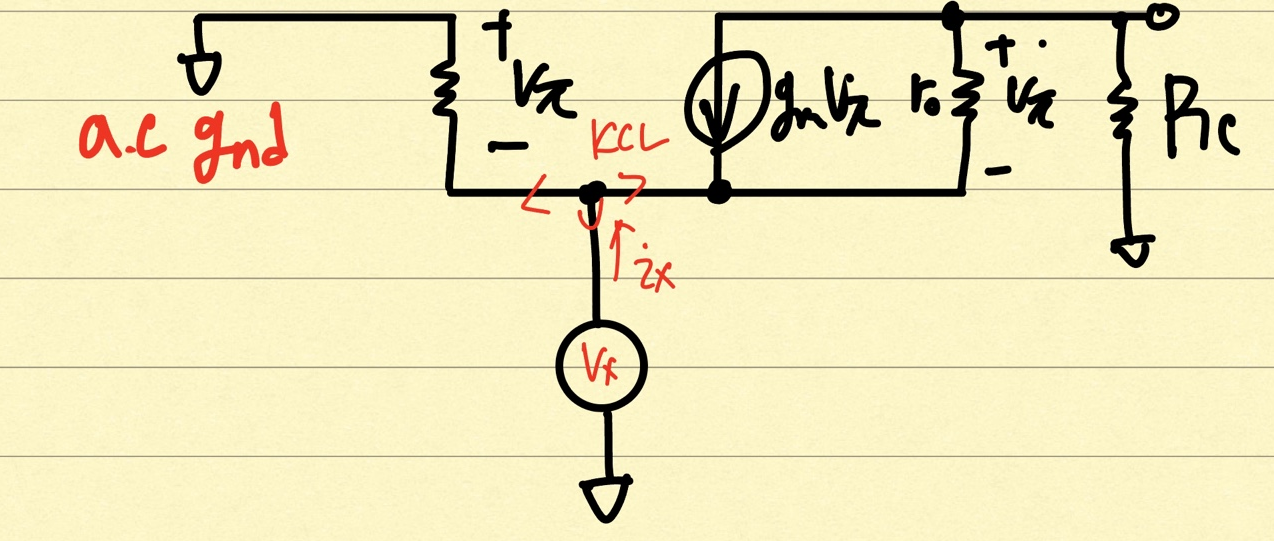

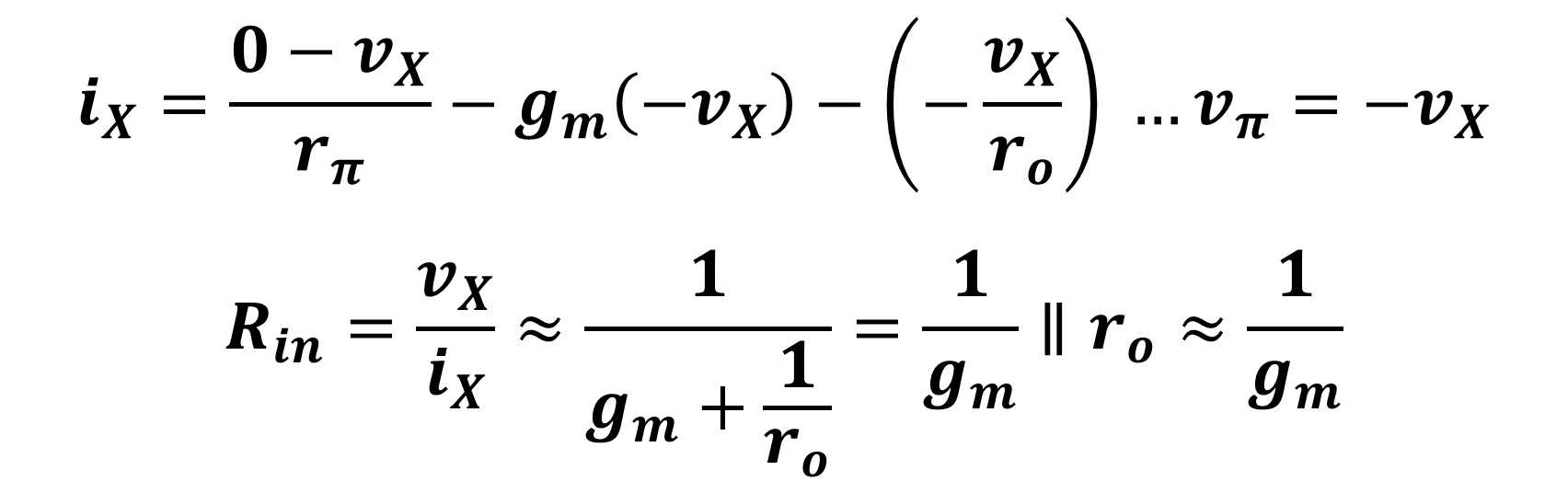

그림 3을 통해 이미터 노드에 KCL을 적용하면 아래와 같다.

식 6에서 Vbe=Vb-Ve의 개념을 상기하고 입력 저항에 대해 표현하면 아래와 같다.

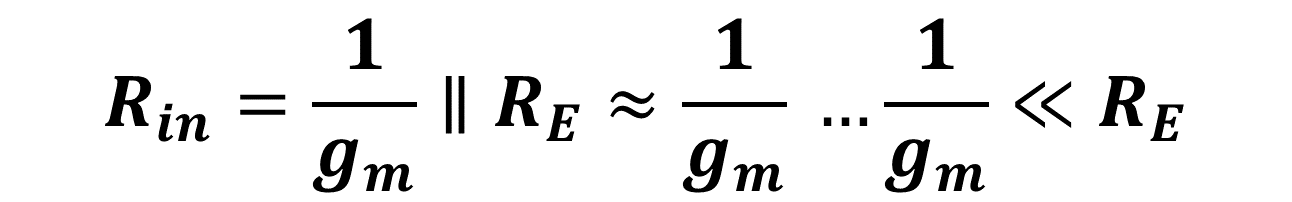

식 7의 1/(r_π)는 무시 가능하다고 가정하면 1/gm으로 표현이 가능하다. 얼리 효과를 고려하게 되면 입력 임피던스는 어떻게 되는지 알아보자

위에서 동일한 방법으로 계산하면 아래와 같은 결과가 나온다.

1/ro 에서 ro도 매우 큰 저항(r_π 보다 훨씬 큰 경우가 많음)이기 때문에 무시 가능함으로 1/gm으로 간략하게 표현이 가능하다.

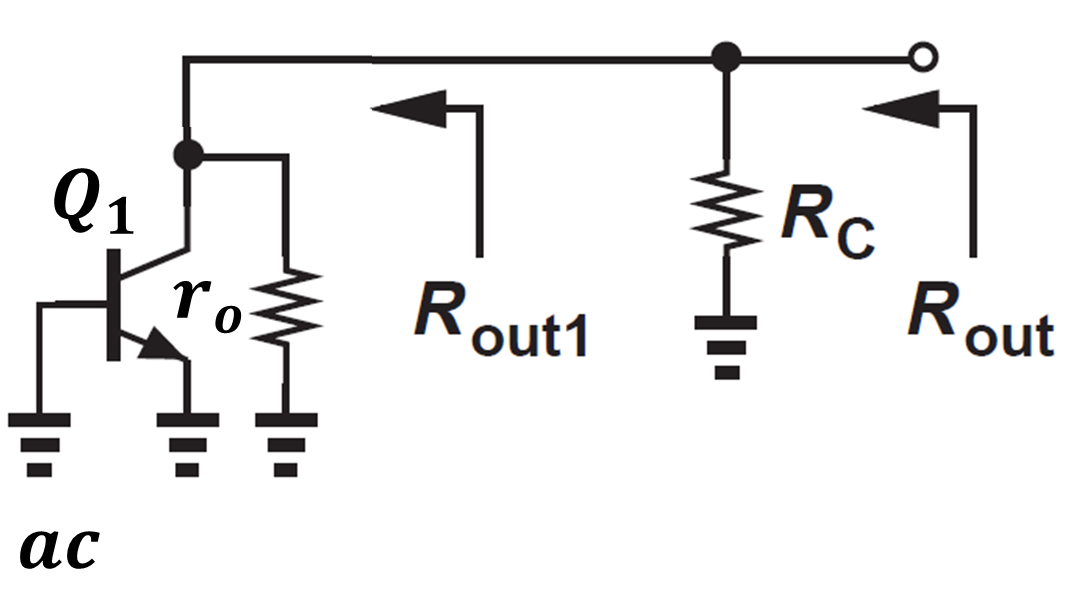

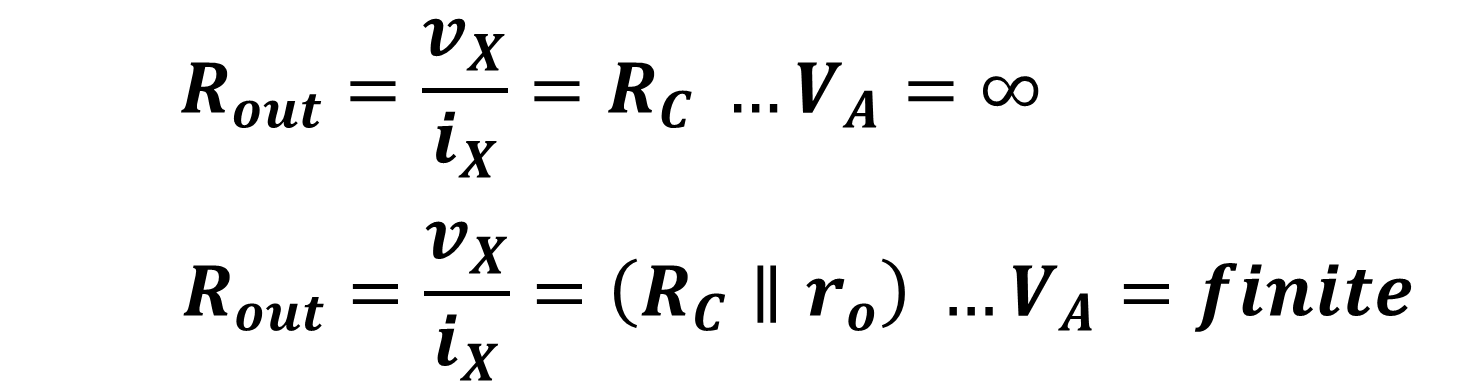

CB core의 출력 저항 또는 임피던스 [Output resistance (or impedance) of CB core]

CB core의 출력 저항은 공통 이미터 코어의 출력 저항과 다른게 없다.

따라서 그림 5의 출력 저항은 아래와 같다.

신호 저항이 연결된 공통 베이스 증폭기

(Common Base Amplifier with Source Resistance Connected)

신호 저항이 연결된 구조는 아래 그림 6과 같다.

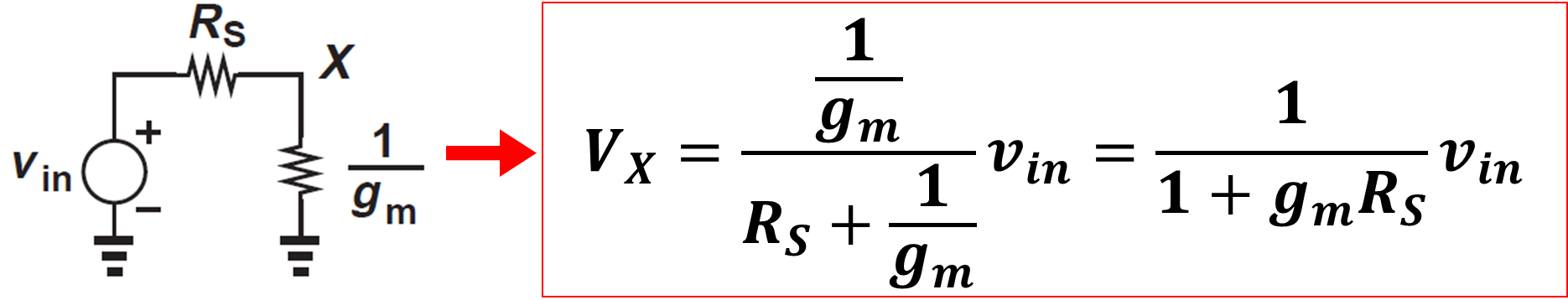

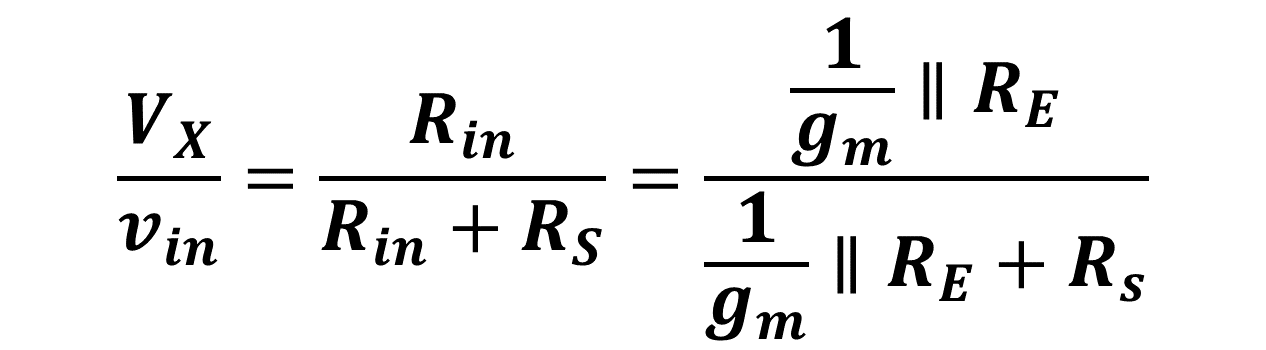

그림 6에서 이미터를 바라본 저항은 1/gm이다 이를 등가하여 노드 X에 걸리는 전압은 아래와 같이 구할 수 있다.

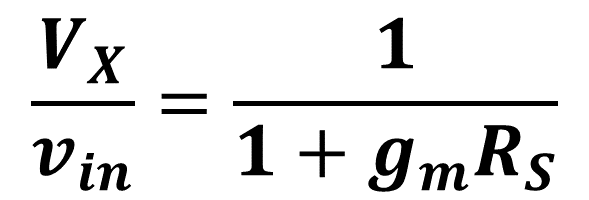

그리고 식 10은 아래와 같이 표현이 가능하다.

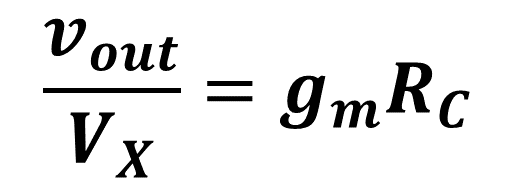

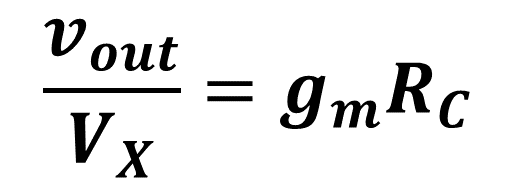

vout/Vx 에 대해서는 공통 베이스 코어의 전압 이득과 동일함으로 아래와 같다.

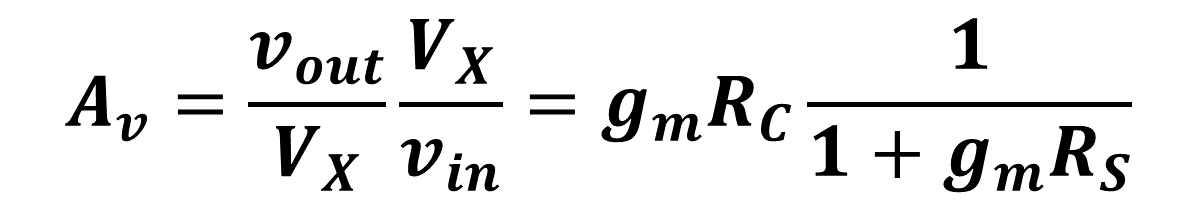

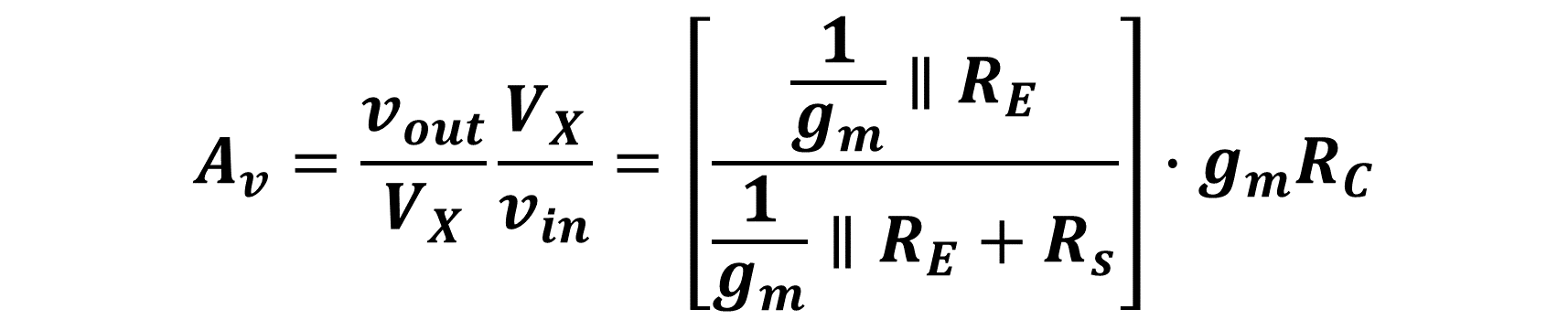

전압 이득은 vout/vin 임으로 Av=(Vx/vin)(vout/Vx) 으로 계산 할 수 있다.

다른 풀이법으로는 이미터 축퇴를 가진 공통 이미터 증폭기에서 구한 방법으로 구할 수 있다. 하지만 식 10-13으로 계산하게 되면 간단하게 해석이 가능하다.

아래 링크에는 다른 풀이법을 볼 수 있다.

공통 이미터 증폭기(Common-Emitter Amplifier)에 대해 알아보자(이미터 축퇴 공통 이미터 증폭기까지)

공통 이미터 (Common-Emitter) 공통 이미터 구조는 아래 그림 1과 같다. 공통 이미터(CE, Common-Emitter)는 입력을 베이스 단자에 인가하고 출력은 콜렉터 단자에서 나온다. 이미터가 공통 접지 되어 있기

doctorinformationgs.tistory.com

bjt 증폭기 특성상 다양한 구조가 있는데 중요한 것 몇개만 다루도록 하겠다.

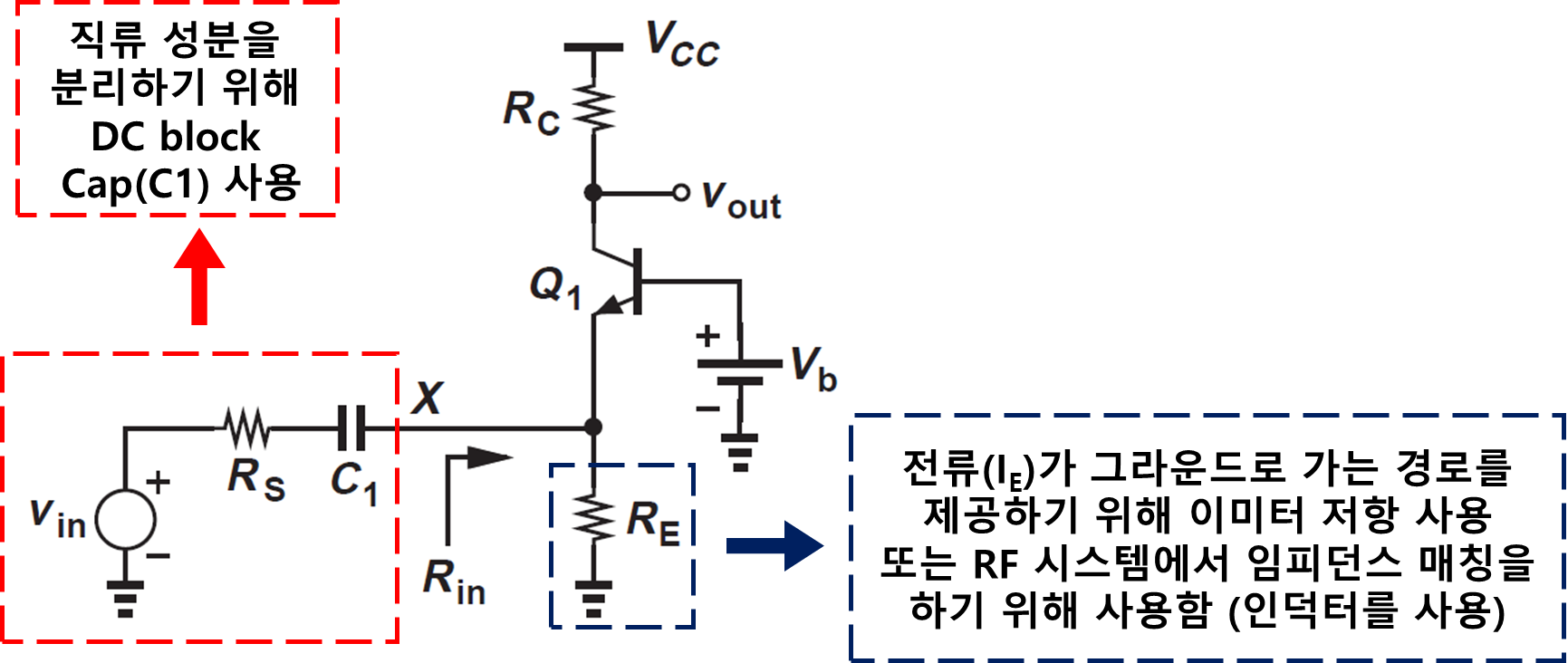

바이어스가 된 공통 베이스 증폭기

여기서 바이어스가 되었다의 의미는 기존에 코어 해석에서 vin은 dc성분이 없고 오직 ac 성분이 있바이어스가 인가된 공통베이스 증폭기의 구조는 아래와 같다.

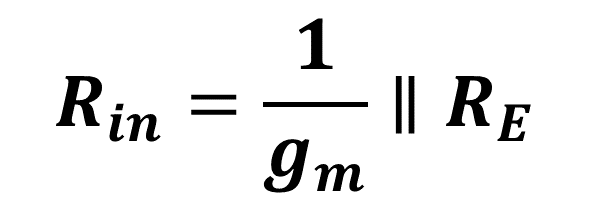

입력 임피던스에 대해서는 이미터를 바라본 저항은 1/gm과 RE와 병렬 연결로 보인다. 따라서

그리고 X노드에 걸리는 소신호 전압 Vx에 대해서는 아래와 같이 인가된다.

공통 베이스 코어의 전압(vout/Vx)는 아래와 같음으로

전압이득은 아래와 같다.

식 17로 인해 알 수 있는 점은 입력 신호 전류가 RE를 통해 접지 되어버린다면 신호를 낭비하게 된다.

(노드 X에서 KCL을 한다면 왜 전류가 낭비 되는지 알 것이다.)

따라서 신호가 낭비되지 않게 입력 임피던스는 아래와 같은 조건을 맞추어야 한다.

전자회로 1 과정을 학습하셨습니다.

아래 링크를 통해 다음 진도와 전자회로 1의 모든 내용을 확인하실 수 있습니다.

2022.01.13 - [전공(Major)/전자회로 1 과정] - 전자회로 1 커리큘럼

전자회로 1 커리큘럼

전자회로 1 커리큘럼입니다. 기본적으로 반도체 공학에서 배웠던 능동소자(Diode, BJT, MOSFET)를 통해 단일 증폭기를 설계한다. 회로를 해석하는데에 있어 회로이론에서 배운 회로 해석기법을 사용

doctorinformationgs.tistory.com

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| BJT 전류 거울(BJT current mirror, CM)에 대해 (0) | 2023.07.06 |

|---|---|

| 배전압기 또는 전압 배가기 (Voltage Doubler) 에 대해 알아보자 (0) | 2023.04.28 |

| 공통 이미터 증폭기 이론(Common-Emitter Amplifier)(코어해석부터 축퇴저항까지) (0) | 2023.03.27 |

| BJT 바이어스 회로를 알아보자 (BJT bias circuits) (0) | 2023.03.24 |

| 회로 내에서의 잡음 표현 (0) | 2023.03.22 |

댓글