이상적인 다이오드로 가정하여 회로를 해석한다.

커패시터의 기본 성질에 대해

계단 신호가 인가된 커패시터 회로

아래 그림 1은 계단 신호가 인가된 경우이다.

커패시터의 두개의 평판 중 하나는 +Q로 충전이 되고 다른 반대의 평판은 -Q로 충전이 된다. 따라서 커패시터 양단에 걸리는 전압은 0이고 출력 전압은 KVL에 의해 구해질수 있다 따라서

왜 출력 전압과 입력 전압이 같을까? 이에 대한 답은 Vc1은 양옆 노드[Vin(+), Vout(-)]에 전압 차이를 가진다. 그림 1과 같이 ΔV 만큼 인가가 된다면

커패시터-다이오드 회로

1) C - 순방향 D

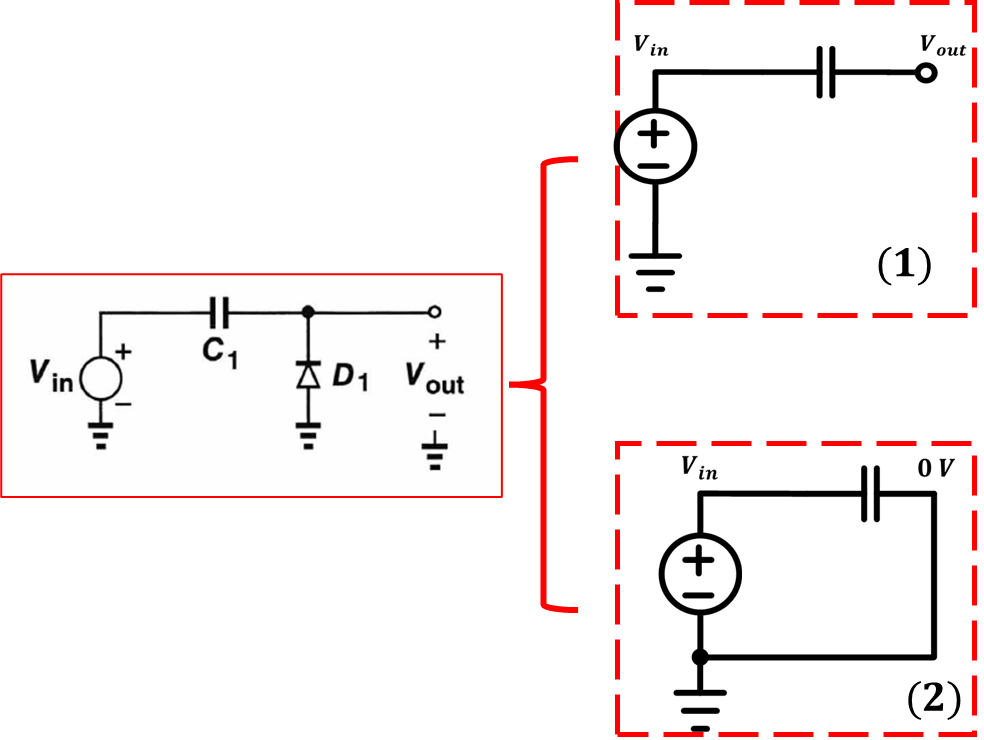

커패시터와 순방향으로 연결된 다이오드는 아래와 같다.

입력 전압(Vin)이 상승할 때 C1 양단에 걸리는 전압도 상승을 하고, 이는 D1을 Turn on 시킴으로써 다이오드는 등가적으로 short이 된다. 이로 인해 C1의 한쪽은 Vin의 전압 반대쪽은 0V를 제공하게 된다. (short이 되는 배선이 그라운드에 연결 되어 있기 때문에) 이에 대해서는 그림 3과 같이 표현되어 있다.

따라서 Vout = 0 V를 가진다. 양의 주기 peak 값에서 음의 주기로 내려갈 때 어떻게 될까?

위 그림 1, 식 1에서 알 수 있는 점은 Cap에 양 끝 판의 전압은 서로 따라감을 알려주는 것을 알 수 있었다. 그리고 전압이 양의 peak까지 올라 갈 때도 양 끝 두 판은 전압을 따라가지만 반대편이 접지에 연결이 되어 출력 전압은 0V를 유지함을 그림 3에서 알 수 있었다. 하지만 양의 peak에서 전압이 내려감으로써 cap의 한쪽판에서 전압이 내려가면 다른 한쪽 판도 따라 내려가기 때문에 Vout에 위치한 cap의 전압은 음으로 떨어진다. 음으로 떨어짐으로써 음의 전압을 제공하고 다이오드는 off로 내려가고 입력전압이 0으로 떨어지면 Vout은 -Vpeak를 달성하고 입력전압이 음의 peak를 달성하게 될 때 Vout은 -2Vpeak를 제공한다.

위에 대한 설명들을 종합한 결과는 아래 그림 5를 통해 볼 수 있다.

2) C - 역방향 다이오드

그림 2와 같은 회로에서 다이오드의 방향을 바꾸게 되면 어떻게 되는지 알아보자. D1이 ON/OFF를 하게되면 그림 3,4와 같아짐을 상기하자

(1) 을 만들기 위해서는 Vin이 양의 전압일 때

(2) 를 만들기 위해서는 음의 전압이 인가 될 때이다.

(2)를 좀 더 자세히 설명하게 되면 Vin이 음의 전압이 인가됨으로써 다이오드는 켜지고 출력 전압 Vout에 0V를 제공한다. 음의 전압이 peak를 달성하고 양의 전압으로 올라갈때 cap 반대편 판에 양의 전압을 제공함으로써 D1은 off가 되어 등가적으로 개방이 된다. 입력 전압이 원점을 지나갈때 출력 전압은 Vpeak가 되고 입력 전압이 양의 peak를 달성하면 출력 전압은 2Vpeak를 제공하게 된다. 이에 대한 결과는 아래 그림 7로 설명할 수 있다.

그림 5와 그림 7의 구조를 보게 되면 입력전압을 고정시키지 못하고 시간에따라 변화함을 알 수 있는데. 이를 고정해주기 위해서 피크 검출기(Peak Dectector)가 필요하다. 이는 반파 정류기에서 배웠기 때문에 아래 링크를 남겨두도록 한다.

2022.02.26 - [회로 관련 전공/회로 과정 통합 글] - 반파 정류기와 전파 정류기(Half- & Full-Wave Rectifier)에 대해 완벽하게 알아보자

반파 정류기와 전파 정류기(Half- & Full-Wave Rectifier)에 대해 완벽하게 알아보자

이 글은 다이오드 회로에서의 네번째 진도입니다. 이번 진도는 대신호 해석이 주(main)가 됨으로 이해하는데에 어려움이 있다면 아래 링크를 통해 참고 바랍니다. 2021.10.02 - [회로 관련 전공/회로

doctorinformationgs.tistory.com

3) 커패시터 분할 회로

임피던스에 걸리는 전압 분배 법칙은 아래와 같다.

따라서 커패시터 회로망에 걸리는 전압도 분배되어 걸린다는 것을 알 수 있다. 아래 그림 8을 보도록 한다.

그림 8의 출력 전압에 대해서는 아래와 같다.

정리하게 되면

커패시터 분할회로는 저항 분할 회로와 달리 C1에 인가되는 전압에 따라 달라짐을 확인 할 수 있다.

4) 전압 배가기(Voltage Doubler or Voltage multiplier)

전압 배가기의 구조는 아래 그림 9와 같다.

동작에 대한 순서는 아래와 같다.

(1) Vin이 음의 전압으로 내려갈 때 ~ 음의 전압 peak를 달성 할 때

(2) 음의 전압 Peak에서 양의 전압으로 올라갈 때 ~ 양의 전압 Peak를 달성할 때

(3) 양의 전압 Peak ~ 원점일 때

(4) (1) 를 반복 할 때

(5) (2)를 반복할 때

(1) Vin이 음의 전압으로 내려갈 때 ~ 음의 전압 peak를 달성 할 때

이에 대한 동작 원리는 그림 6의 (2)와 동일하다. D1이 단락, D2는 개방이 되면서 C1의 오른쪽 판에는 0 V를 제공하게 된다. 이는 그림 10과 같다.

(2) 음의 전압 Peak에서 양의 전압으로 올라갈 때 ~ 양의 전압 Peak를 달성할 때

그림 6의 (1)과정이 진행이 되면서 C1의 오른쪽 판에서 2Vpeak를 제공하게 되고 C1의 오른쪽 판이 양의 전압을 제공하면서 D2가 turn on이 된다. 이로인해 출력 전압노드에서 식 5를 통해 계산이 가능하다 C1=C2인 경우

출력 전압에 1*Vpeak를 제공한다.

(3) 양의 전압 Peak ~ 원점일 때

출력 전압 노드는 1Vpeak임으로 C2는 해당 전압을 충전하게 되고 D2 양단의 전압차는 0이 됨으로 D2는 다시 꺼진다. 해당 구간에서는 D1, D2 둘다 Open 상태이다.

(4) (1) 를 반복 할 때

그림 10과 동일하게 C1의 오른쪽 판은 2Vpeak까지 충전한다.

(5) (2)를 반복할 때

양의 Peak를 도달함으로써 D2의 애노드는 2Vpeak, 캐소드는 1Vpeak(C2에 의해)의 전압 차를 가지고 있다 1Vpeak 만큼의 전압이 제공이 되고 식 5를 통해 출력 전압은

위 과정을 다시 반복함으로써 출력 전압은 최종적으로 2Vpeak를 제공한다.

(1) ~ (5) 까지의 과정을 표현하면 아래 그림 13과 같다.

전자회로 1 과정을 학습하셨습니다.

아래 링크를 통해 다음 진도와 전자회로 1의 모든 내용을 확인하실 수 있습니다.

2022.01.13 - [전공(Major)/전자회로 1 과정] - 전자회로 1 커리큘럼

전자회로 1 커리큘럼

전자회로 1 커리큘럼입니다. 기본적으로 반도체 공학에서 배웠던 능동소자(Diode, BJT, MOSFET)를 통해 단일 증폭기를 설계한다. 회로를 해석하는데에 있어 회로이론에서 배운 회로 해석기법을 사용

doctorinformationgs.tistory.com

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| 바이폴라 차동쌍의 대신호 해석(Large signal analysis of BJT differential pair) (0) | 2023.07.11 |

|---|---|

| BJT 전류 거울(BJT current mirror, CM)에 대해 (0) | 2023.07.06 |

| 공통 베이스 증폭기 이론(Common-Base Amplifier) (0) | 2023.04.07 |

| 공통 이미터 증폭기 이론(Common-Emitter Amplifier)(코어해석부터 축퇴저항까지) (0) | 2023.03.27 |

| BJT 바이어스 회로를 알아보자 (BJT bias circuits) (0) | 2023.03.24 |

댓글