해당 글은 전류 거울의 2번째 진도이다.

MOS 전류 거울 포스팅에서 저항 분할 회로가 가지는 문제점을 언급하였으니 해당 글은 간단한 결과만 언급하도록 한다.

공정 전압 온도 변이 (Process Voltage Temperature variation, PVT variation)

| 종류 | 무엇과 연관이 되어 있을까? | 어떤 결과를 가져올까? |

| Vcc | 공급전압에서 ripple과 noise가 생기는 경우 | 저항 바이어스 회로를 구성할 때 공급전압의 변화는 컬렉터 전류의 변화를 초래한다. |

| 저항 | 공정 | 저항 바이어스 회로를 구성할 때 저항 값이 달라지면 베이스 전압이 달라짐으로 이는 컬렉터 전류의 변화를 초래한다. |

| Is | 온도 | 온도에 따라 컬렉터 전류가 변화함 |

| Vt(열 등가 전압) | 온도 | Vt=(kT/q)임으로 온도가 변하면 Vt도 변한다. |

MOS 전류 거울에 대해서는 아래 링크에 대해 언급 되어있다.

2021.10.28 - [회로 관련 전공/회로 과정 통합 글] - 전류 거울(Current Mirror)의 원리를 알아보자

전류 거울(Current Mirror)의 원리를 알아보자

전류 거울은 집적회로를 설계할 때 아주 유용한 기법 중 하나이다. 왜 이런 기법이 유용한지에 대해서 알아보고, 하나하나 알아가 보면서 완벽히 이해해보도록 하기 전에 공정 변화(또는 변이, P

doctorinformationgs.tistory.com

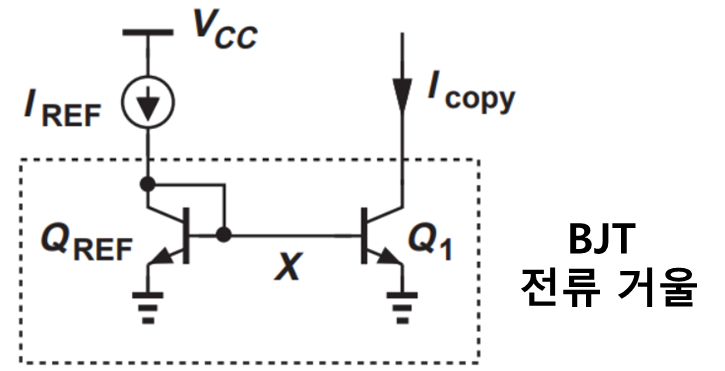

BJT 전류 거울 (BJT Current Mirror)

1. 베이스 전류와 얼리 효과를 고려하지 않는 경우

BJT 전류 거울은 아래와 같이 구성되어 있다.

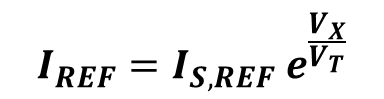

베이스 전류(IB)를 무시하기 때문에 레퍼런스 전류는 아래와 같이 표현이 가능하다.

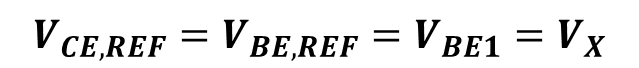

그리고 Q,REF의 베이스 전압(Vx)에 대해서는 아래와 같이 표현이 가능하다.

그림 1에서 Qref와 Q1은 같은 전압을 가지고 있음으로 아래와 같이 표현이 가능하다.

그리고 Q1의 전류에 대해서는 아래와 같다.

식 4에 식 2를 대입하게 되면

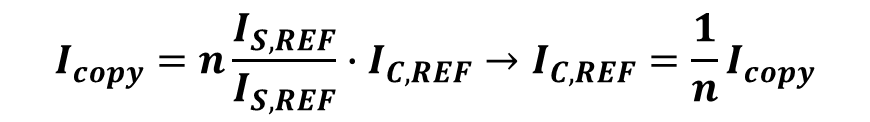

따라서 복사 전류에 대해서 아래와 같이 표현이 가능하다.

식 6이 의미하는 것은 복사 전류는 기준 전류(Iref)와 Q1과 Qref의 역포화 전류(Is) 비에 따라 전류의 양이 정해진다. 식 6은 온도에 따른 전류 변화가 없음(Vt가 없음으로)을 알려주고 있다. Is도 온도에 의존하는 함수이지만 (n_i)^2 항이 서로 소거 되기 때문에 온도에 무관함을 알 수 있다.

여기서 n배 만큼 복사시키려면 어떻게 해야 할까?

Q1을 Qref와 동일한 BJT로 사용하여 병렬연결로 연결 하면 n배 만큼 복사할 수 있다.

2. 베이스 전류의 효과를 고려한 경우 (얼리 효과 고려 x)

그림 1에서 베이스 전류를 고려하여 그림 2와 같이 표현하였다.

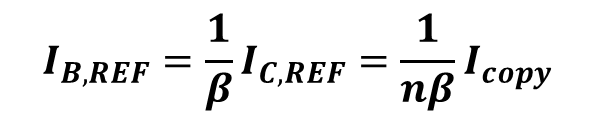

쉽게 이해하기 위해 복사 전류부터 접근하여 보도록 한다. 먼저 위에서 n배 복사 하기 위해선 Q1을 Qref와 동일한 트랜지스터를 n개 사용하면 n배 복사함을 상기하고 복사전류(Icopy)와 REF 트랜지스터의 컬렉터 전류에 대해서는 아래와 같이 다시 표현이 가능하다.복사 전류(Icopy)와 해당 BJT의 베이스 전류에 대해서는 아래와 같이 표현이 가능하다.

그리고

복사전류(Icopy)의 베이스 전류에 대해서는 아래와 같이 표현이 가능하다.

그리고 식 8을 통해 REF 트랜지스터(Qref)의 베이스 전류도 아래와 같이 표현이 가능하다.

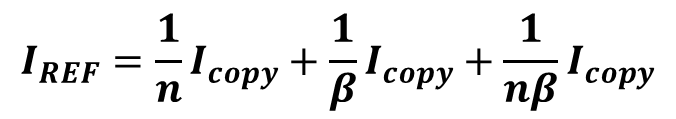

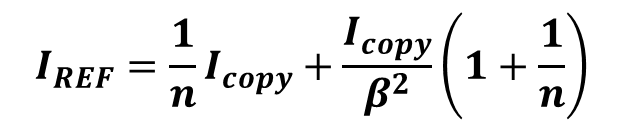

그림 2에서 Vx 노드에 KCL 을 적용하면 아래와 같다.

식 8 ~ 10 을 식 11에 대입하면

식 12를 복사 전류(Icopy)에 대해 표현하면 아래와 같이 얻어 질 수 있다.

식 13을 통해 알 수 있는 점은 큰β와 적절한 n인 경우에 식 13은 식 8인 Icopy는 대략적으로 nIref로 표현이 가능하다.

n이 증가함에 따라 오차가 커지는 문제점이 발생한다.

베이스 전류 오차를 줄이기 위한 회로

베이스 전류의 오차를 줄여주기 위한 회로는 아래 그림 3과 같이 구현하면 된다. 간단한 해석을 위해 이미터 폴로워의 이미터 전류는 대략적으로 컬렉터 전류와 같다고 표현한다.

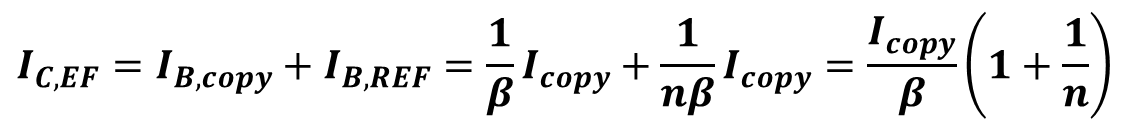

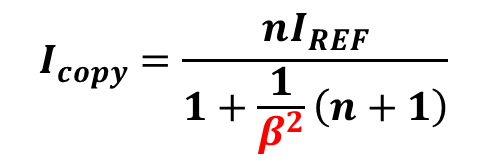

노드 X에서 KCL을 적용하면 아래와 같이 표현이 가능하다.

그리고 이미터 폴로워 베이스 전류에 대해서는 아래와 같다.

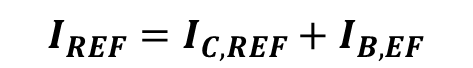

그리고 노드 P에서 KCL을 적용하면 아래와 같이 표현이 가능하다.

식 15, 식 8을 식 16에 대입하면

그리고 복사 전류에 대해 표현하면 아래와 같다.

식 13과 식 18을 비교해보면 β에서 β 제곱이 되면서 오차를 많이 줄일 수 있음을 알 수 있다. (통상적으로 β=100 ~ 200 사이의 값을 가짐을 상기하자)

전자회로 2 과정을 학습하셨습니다.

아래 링크를 통해 다음 진도와 전자회로 2의 모든 내용을 확인하실 수 있습니다.

2022.01.12 - [전공(Major)/전자회로 2 과정] - 전자회로 2 커리큘럼

전자회로 2 커리큘럼

전자회로 2 커리큘럼입니다. 전자회로 2에 대한 간략한 설명은 아래와 같습니다. 전자회로 1에서 배웠던 능동소자(Diode, BJT, MOSFET)에 대해 학습했으며 그에 대한 다이오드 회로 및 단일 증폭기인

doctorinformationgs.tistory.com

'회로 관련 전공 > 회로 과정 통합 글' 카테고리의 다른 글

| MOS 차동 증폭기 대신호 해석 (1) | 2023.07.20 |

|---|---|

| 바이폴라 차동쌍의 대신호 해석(Large signal analysis of BJT differential pair) (0) | 2023.07.11 |

| 배전압기 또는 전압 배가기 (Voltage Doubler) 에 대해 알아보자 (0) | 2023.04.28 |

| 공통 베이스 증폭기 이론(Common-Base Amplifier) (0) | 2023.04.07 |

| 공통 이미터 증폭기 이론(Common-Emitter Amplifier)(코어해석부터 축퇴저항까지) (0) | 2023.03.27 |

댓글